**VESA DisplayPort (DP) Standard**

Version 2.0 26 June, 2019

www.vesa.org

## Purpose

The purpose of this document is to define a flexible system and apparatus capable of transporting video, audio and other data between a Source device and a Sink device over a digital communications interface.

## Summary

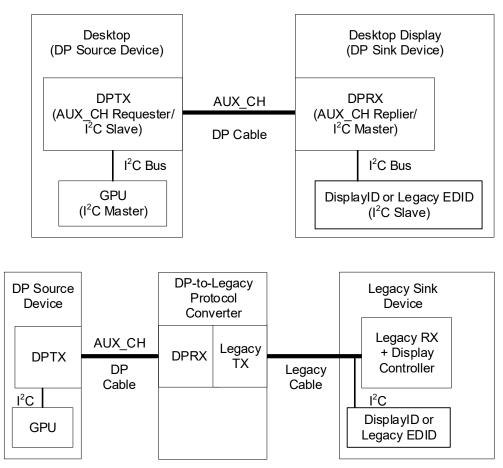

The DisplayPort<sup>™</sup> standard specifies an open digital communications interface for use in both internal connections, such as interfaces within a PC or monitor, and external display connections. Suitable external display connections include interfaces between a PC and monitor or projector, between a PC and TV, or between a device such as a DVD player and TV display.

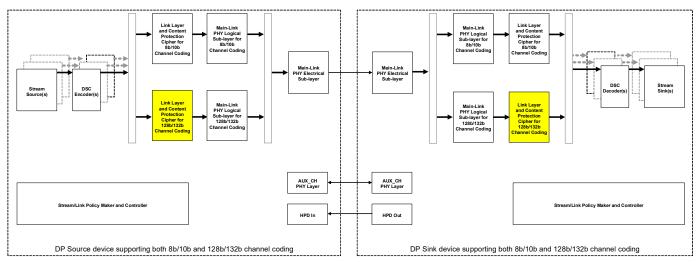

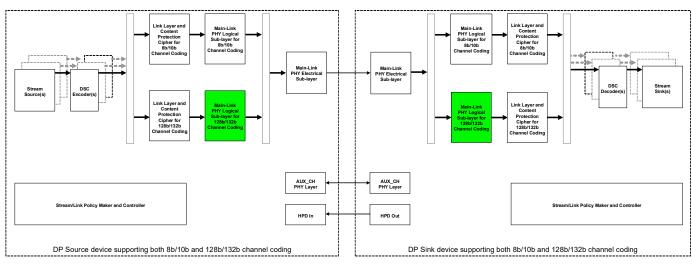

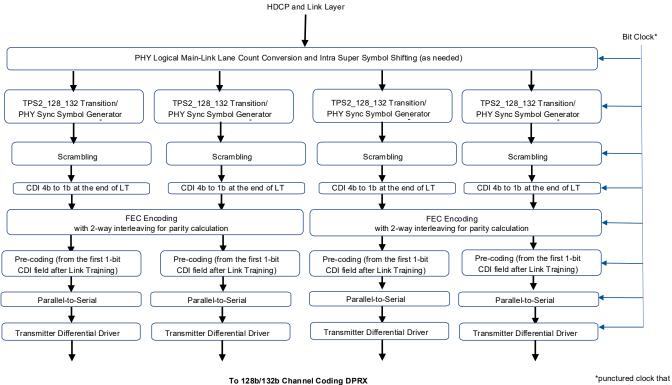

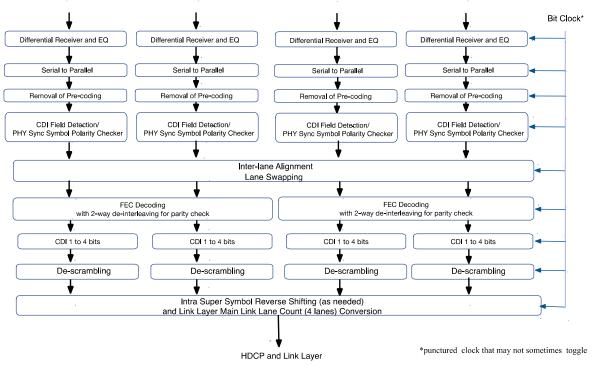

*DP v2.0* adds 128b/132b channel coding and new link rates up to 20Gbps/lane to boost the per-lane link data bandwidth by as much as three times that of HBR3, while maintaining full backward compatibility with *DP v1.4a*. *DP v2.0* also adds Panel Replay mode (based on the Panel Self Refresh 2 mode of *eDP v1.4b* and higher), both for system-level power reduction and for furthering of the Adaptive Sync solution. Furthermore, DSC support is mandated for *DP v2.0* devices that support 128b/132b channel coding for realizing the most deterministic and robust interoperability.

*DP v1.4a* was revised to correct errata items and add reference to *DSC v1.2a* for enabling YCbCr420 support.

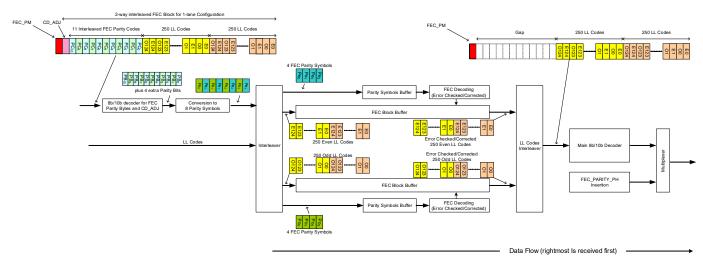

*DP v1.4* was revised to add VESA<sup>®</sup> Display Stream Compression (DSC) transport support for visually lossless 8Kp/10Kp60Hz video along with full extension of audio transport up to 32-channel L-PCM 3D Audio, at 192kHz and HBR 8-channel audio up to 1536kHz. For visual glitch-free DSC bitstream transport, Reed-Solomon (254, 250) Forward Error Correction (FEC) was added. In addition to the sheer video and audio transport bandwidth increase, *DP v1.4* incorporates metadata transport for both static and dynamic High Dynamic Range (HDR). Furthermore, *DP v1.4* enhances the Multi-Stream Transport (MST) feature to better enable multi-function dock supporting DP Alt Mode on USB Type-C.

*DP v1.3* was revised to add 8.1Gbps/lane link rate and living-room friendliness improvement, both for direct connection to a living room display and through DP-to-HDMI protocol converter.

DP v1.2a was revised to correct errata items and add clarifications to DP v1.2.

*DP v1.2* was revised to add enhancements including higher speed operation, more flexible topology management, multiple streams on a single connection, higher speed Auxiliary Channel communications, improved support for audio, and a new smaller connector. It also corrected errors and added clarifications to *DP v1.1a*. This version corrects errors and adds clarification to *DP v1.2*. Furthermore, this version adds DP\_PWR voltage level options to a downstream DP device.

DP v1.1a was revised to correct errata items and add clarifications to DP v1.1.

## Contents

| Purpose   |         |         |                                                             | 2  |

|-----------|---------|---------|-------------------------------------------------------------|----|

| Summary   |         |         |                                                             | 2  |

| Preface   |         |         |                                                             | 32 |

|           |         |         | operty                                                      |    |

|           |         |         |                                                             |    |

|           | Patents | 5       |                                                             |    |

|           |         |         | s Standard                                                  |    |

|           | Ackno   | wledgm  | ents                                                        | 35 |

|           |         | •       | ry                                                          |    |

| Section 1 | Introd  | luction |                                                             | 49 |

|           | 1.1     | Organ   | ization                                                     | 49 |

|           | 1.2     | Displa  | yPort Objectives                                            |    |

|           |         | 1.2.1   | Key Industry Needs for DisplayPort                          |    |

|           |         | 1.2.2   | Technical Objectives                                        | 51 |

|           |         | 1.2.3   | External Connection Objectives                              | 52 |

|           |         | 1.2.4   | Internal Connection Objectives.                             |    |

|           |         | 1.2.5   | CE Connection Objectives                                    | 53 |

|           |         | 1.2.6   | Content Protection                                          | 53 |

|           |         | 1.2.7   | <i>DP v2.0</i> Objectives                                   |    |

|           | 1.3     | Acron   | yms and Abbreviations                                       | 55 |

|           | 1.4     | Glossa  | ıry                                                         | 62 |

|           | 1.5     | Conve   | ntions                                                      | 70 |

|           |         | 1.5.1   | Precedence                                                  | 70 |

|           |         | 1.5.2   | Keywords                                                    | 70 |

|           |         | 1.5.3   | Numbering                                                   | 70 |

|           |         | 1.5.4   | Bit and Byte Ordering Nomenclature                          | 71 |

|           | 1.6     | Refere  | nce Documents                                               | 73 |

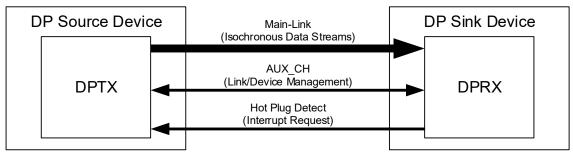

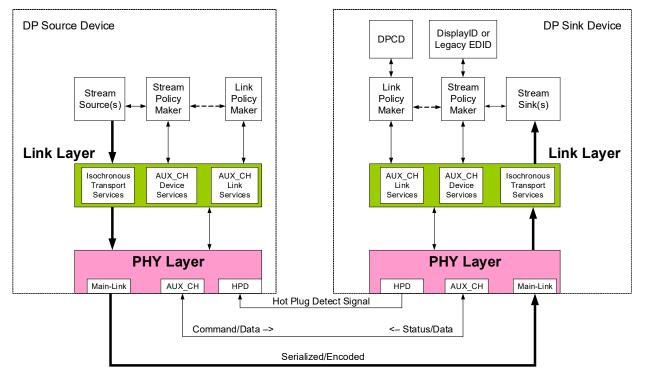

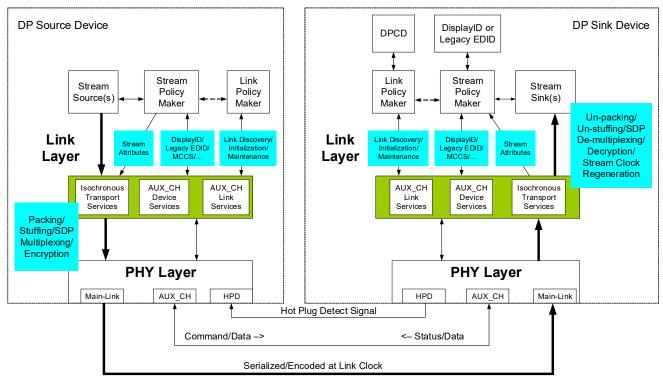

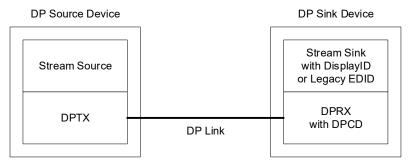

|           | 1.7     | Overv   | iew                                                         | 78 |

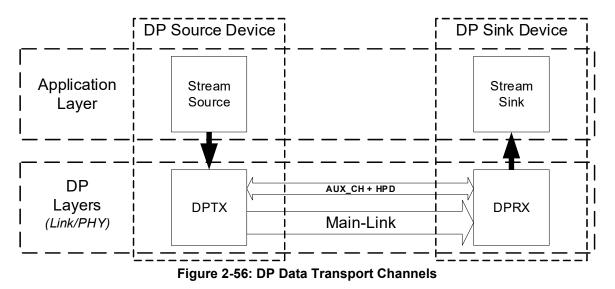

|           |         | 1.7.1   | Main-Link Composition                                       | 79 |

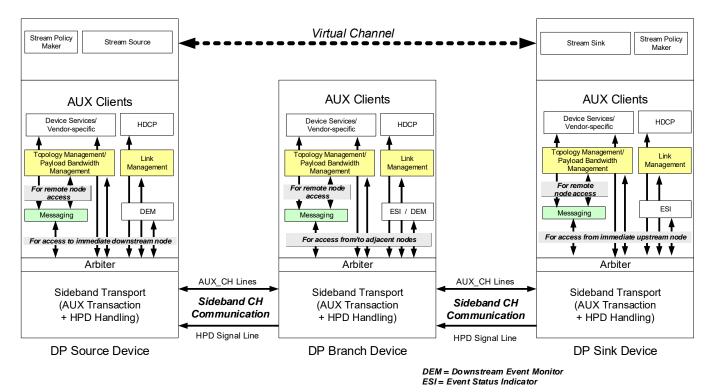

|           |         | 1.7.2   | AUX_CH Composition                                          | 81 |

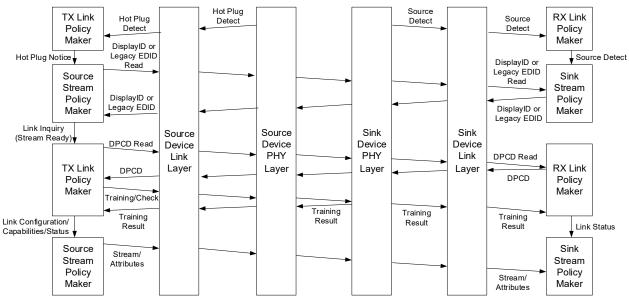

|           |         | 1.7.3   | Link Configuration and Management                           | 81 |

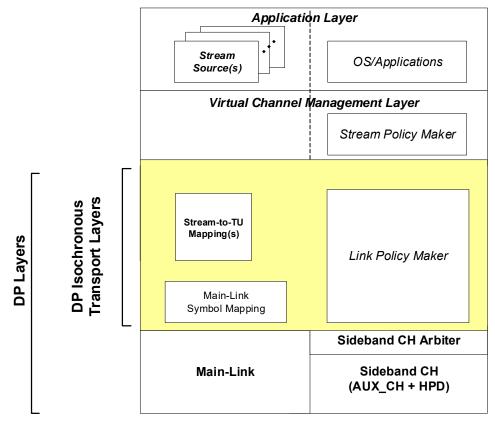

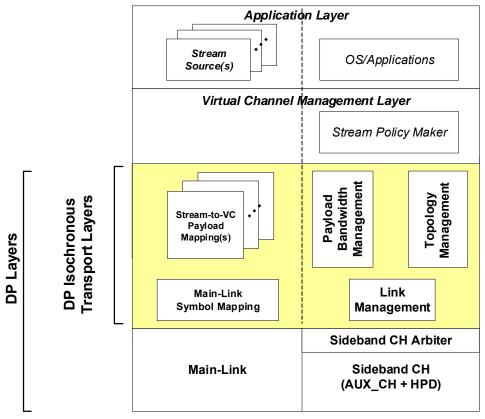

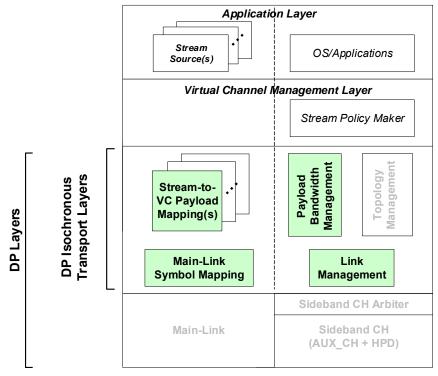

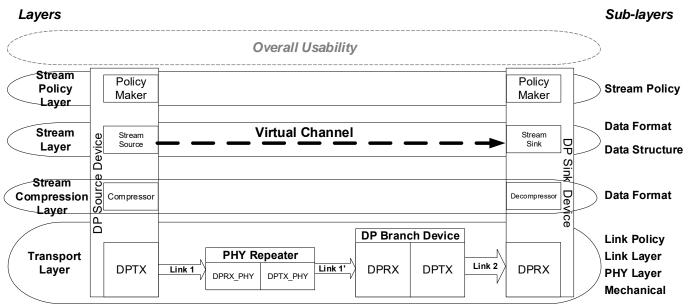

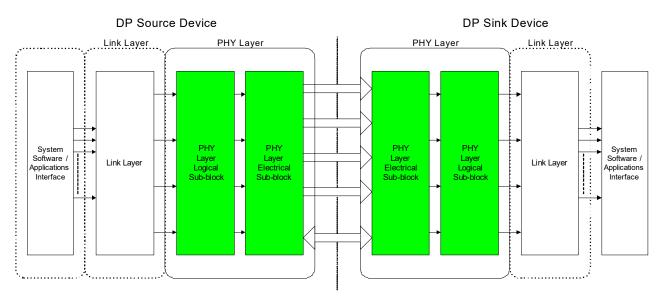

|           |         | 1.7.4   | Layered Modular Architecture                                | 82 |

| Section 2 | Link L  | .ayer S | pecifications                                               | 83 |

|           | 2.1     | SST M   | Iode with 8b/10b Link Layer Introduction.                   | 83 |

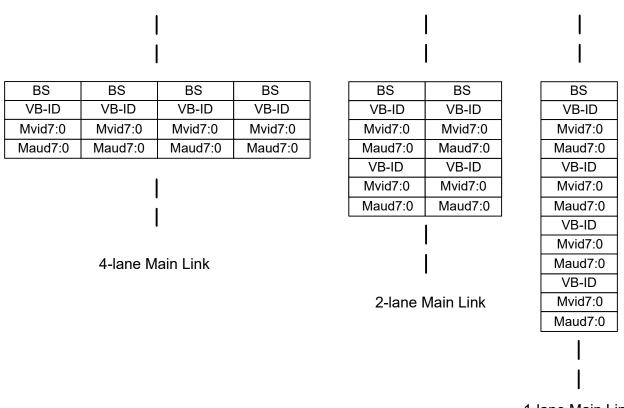

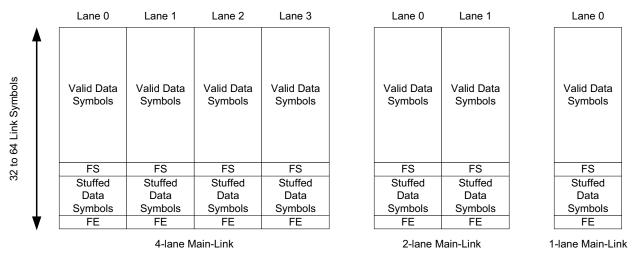

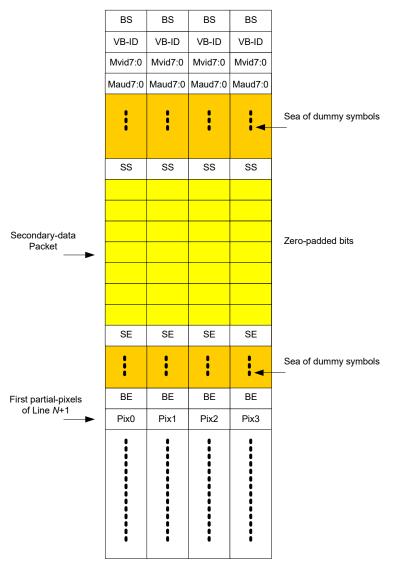

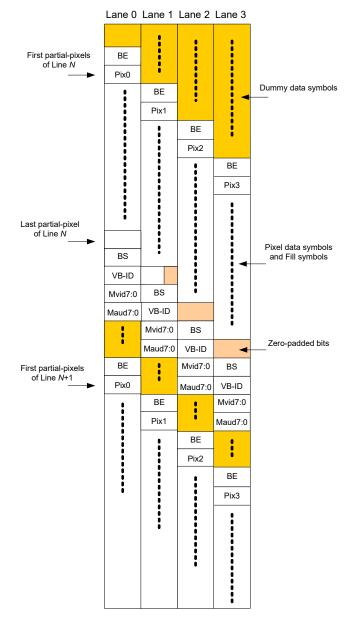

|           |         | 2.1.1   | Number of Lanes and Per-lane Data Rate in SST and MST Modes | 84 |

|           |         | 2.1.2   | Number of Main, Uncompressed Video Streams in SST Mode      | 85 |

|           |         | 2.1.3   | Basic Functions in SST and MST Modes                        | 85 |

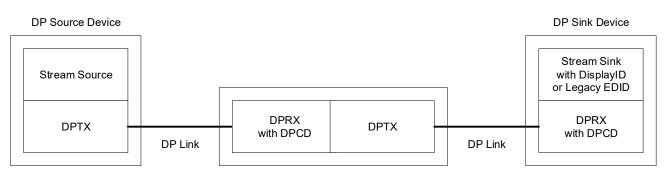

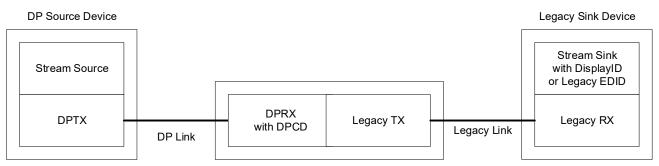

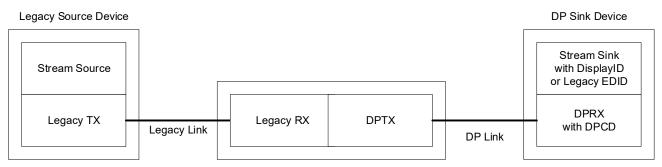

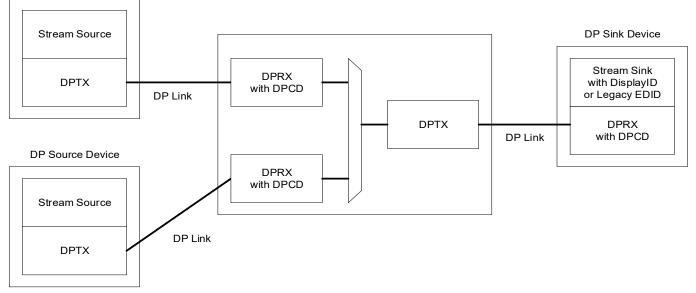

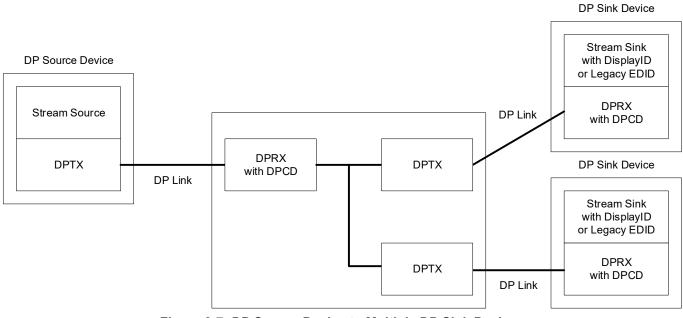

|           |         | 2.1.4   | DP Device Types and Link Topology in SST Mode               | 86 |

| 2.2 |        | onous Transport Services in SST Mode<br>b/10b Link Layer         | 02   |

|-----|--------|------------------------------------------------------------------|------|

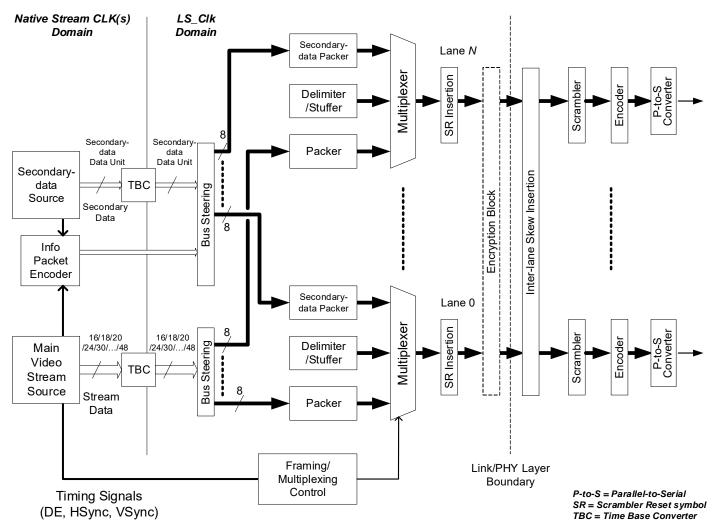

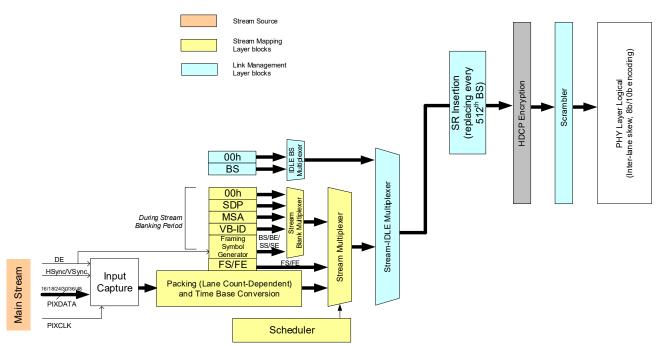

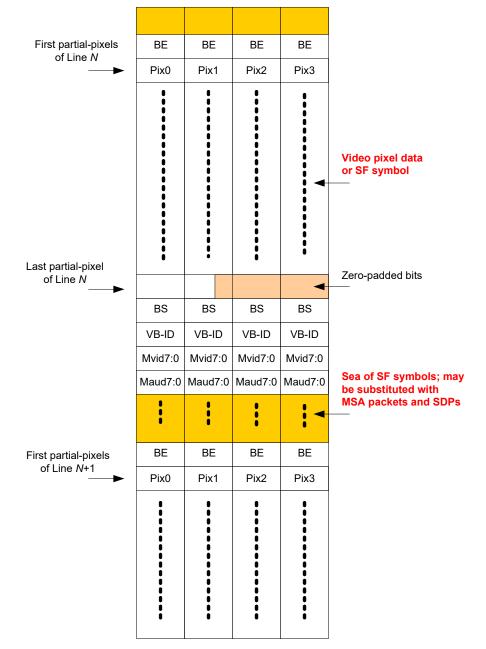

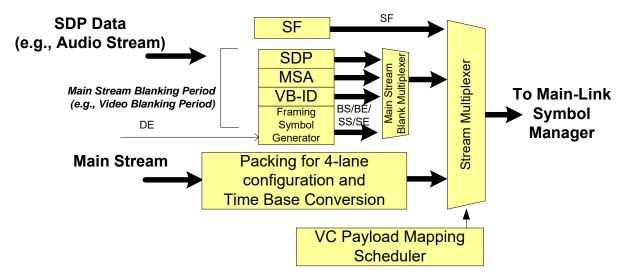

|     | 2.2.1  | Main Video Stream to Main-Link Lane Mapping in the Source Device |      |

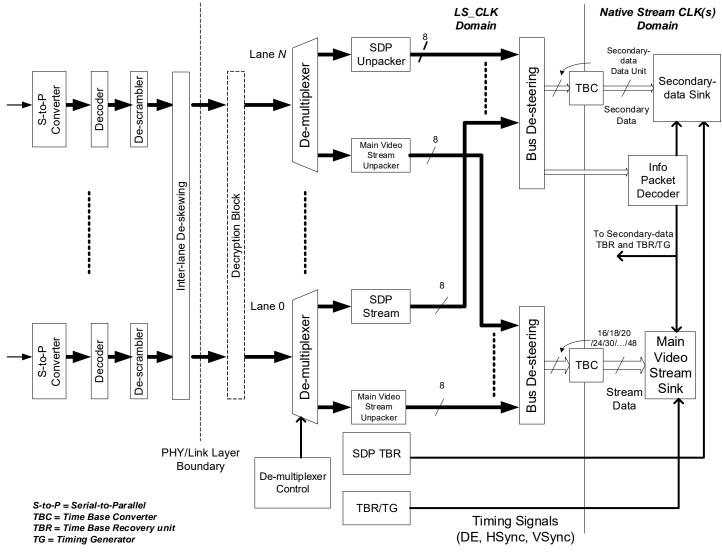

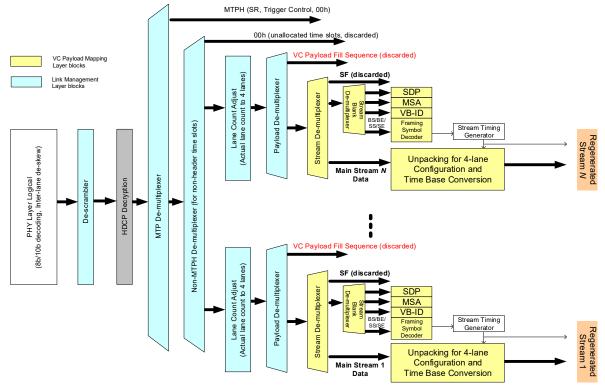

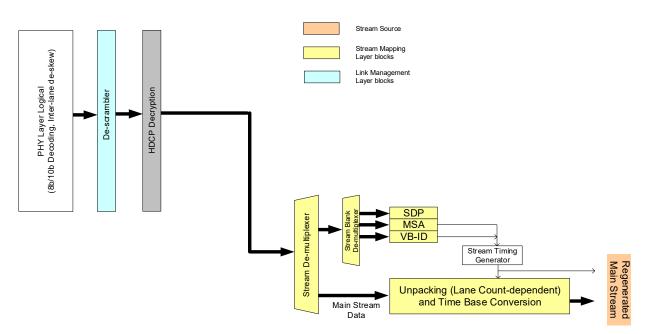

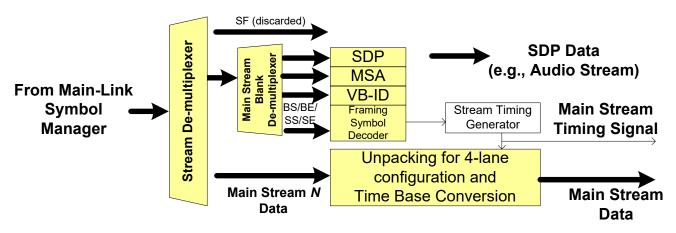

|     | 2.2.1  | Stream Reconstruction in the Sink Device                         |      |

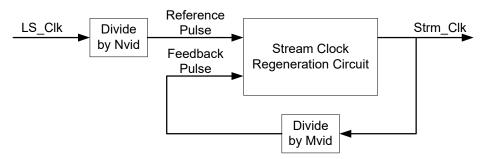

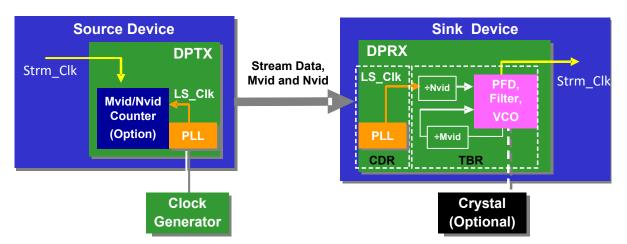

|     | 2.2.2  | Stream Clock Regeneration.                                       |      |

|     | 2.2.3  | MSA Data Transport                                               |      |

|     | 2.2.4  | SDP Formats                                                      |      |

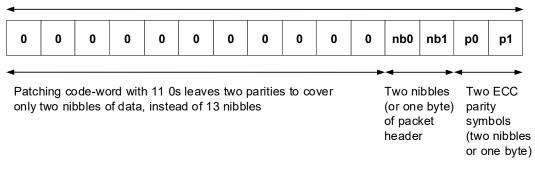

|     | 2.2.5  | ECC for SDP                                                      |      |

| 2.3 | -      | CH States and Arbitration                                        |      |

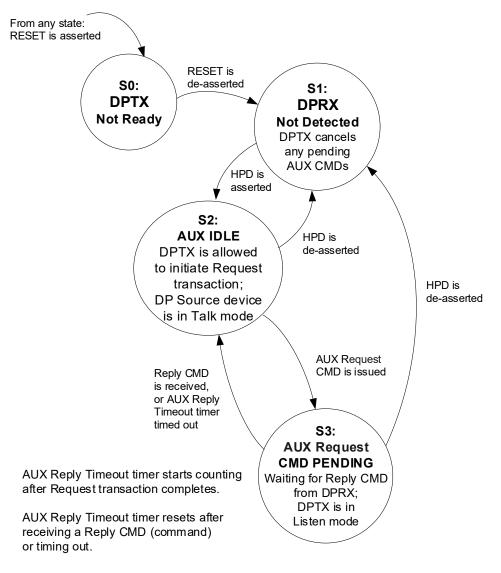

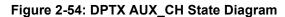

| 2.5 | 2.3.1  | AUX CH States Overview                                           |      |

|     | 2.3.2  | Link Layer Arbitration Control.                                  |      |

|     | 2.3.2  | Policy Maker AUX Services.                                       |      |

|     | 2.3.4  | Detailed DPTX AUX CH State and Event Descriptions                |      |

|     | 2.3.5  | Detailed DPRX AUX CH State and Event Descriptions                |      |

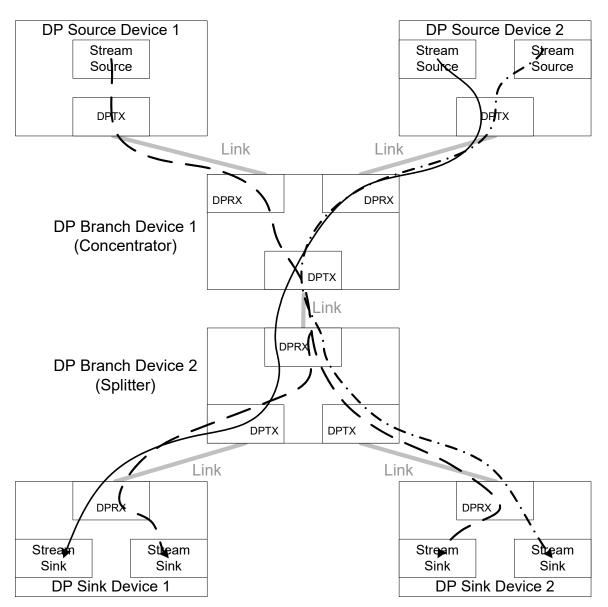

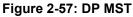

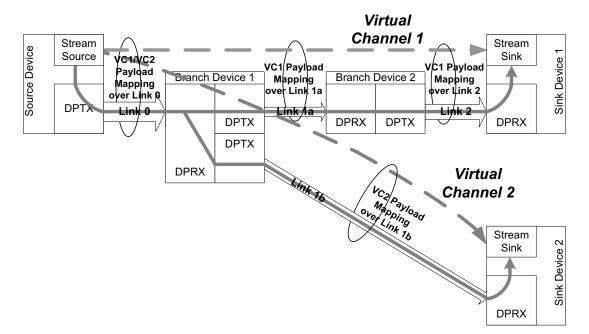

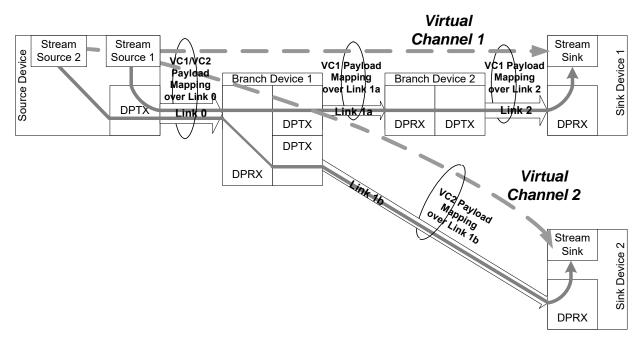

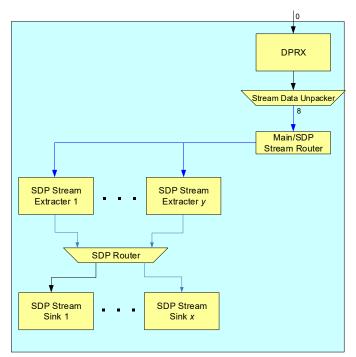

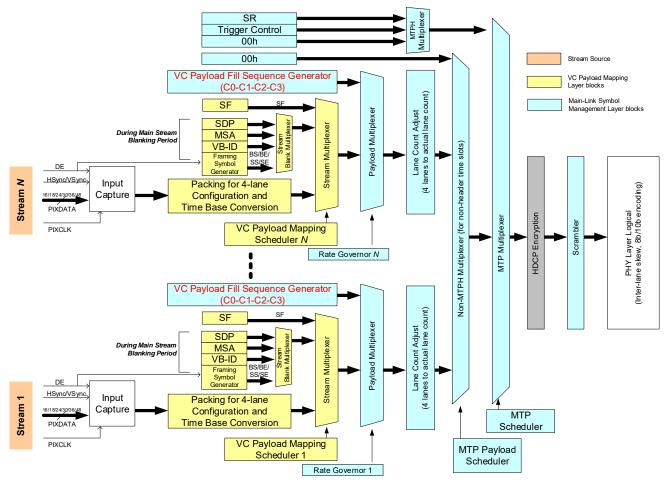

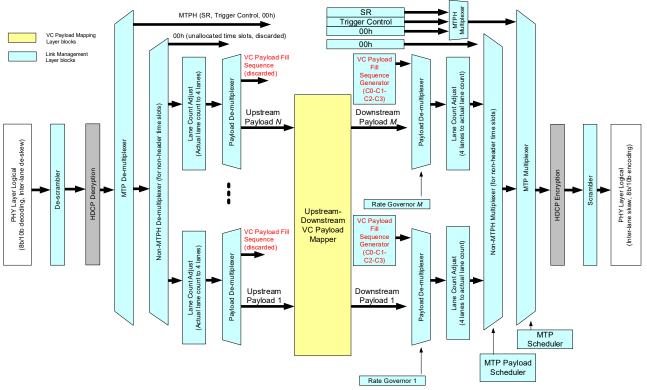

| 2.4 |        | Ilti-stream Isochronous Transport Service Overview               |      |

|     | 2.4.1  | Connection-oriented Transport                                    |      |

|     | 2.4.2  | DP Isochronous Transport Service Layers                          |      |

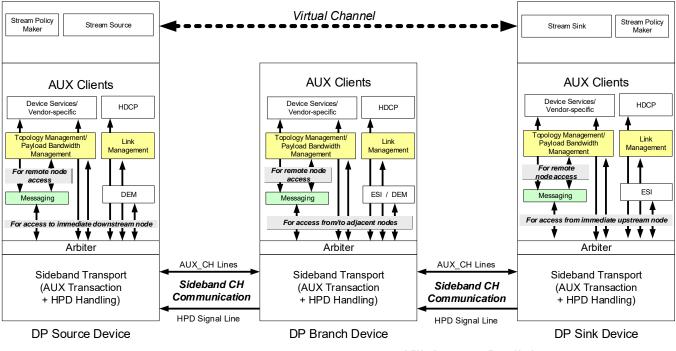

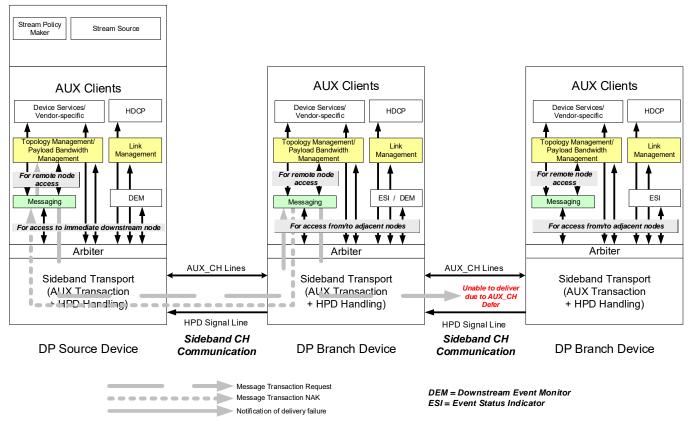

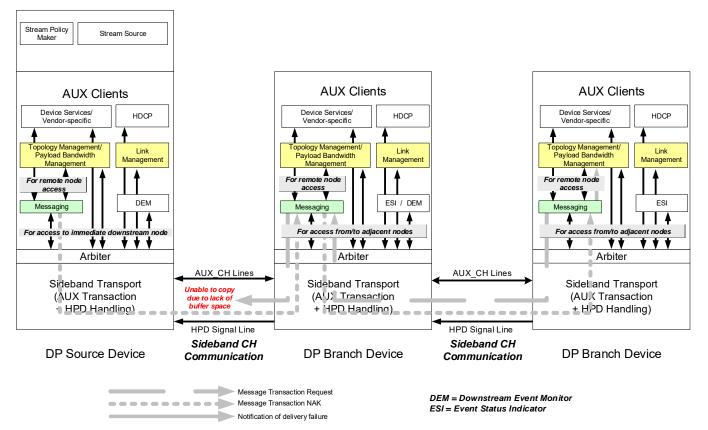

|     | 2.4.3  | Sideband CH Communications                                       |      |

| 2.5 | Topolo | bgy Management Layer                                             |      |

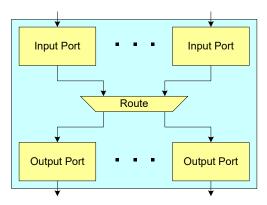

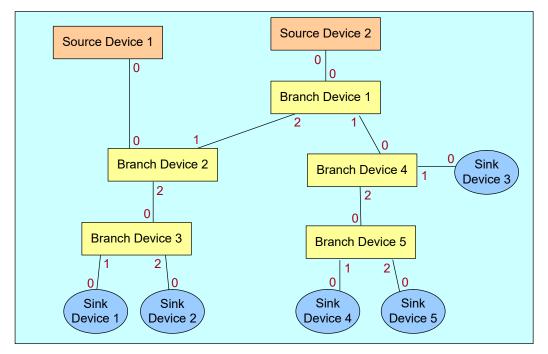

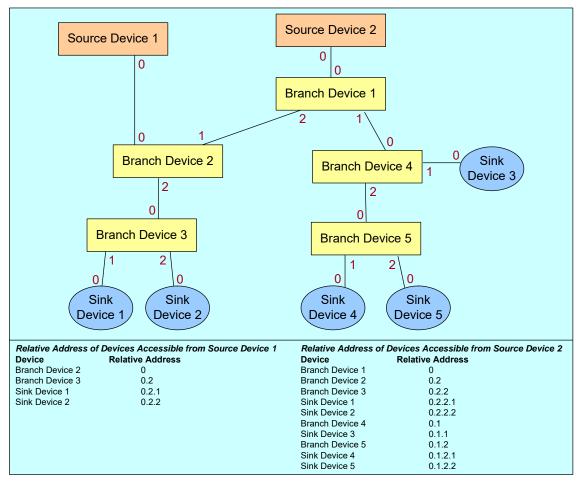

|     | 2.5.1  | Primitives of Multi-stream DP Devices and Device Types           |      |

|     | 2.5.2  | Multi-stream Topologies.                                         |      |

|     | 2.5.3  | Multi-Stream Device Identification                               |      |

|     | 2.5.4  | Topology Manager and Topology Assistant                          | .254 |

|     | 2.5.5  | Topology Discovery                                               | .254 |

|     | 2.5.6  | Topology Maintenance                                             | .255 |

|     | 2.5.7  | Topologies with Single-stream-only Source devices                | .256 |

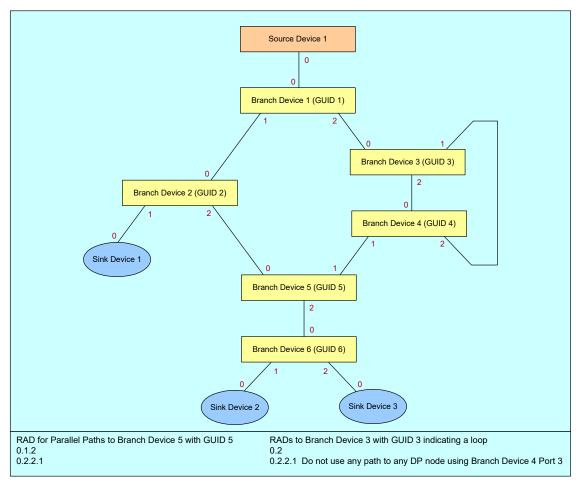

|     | 2.5.8  | Loop Handling                                                    | .257 |

| 2.6 | MST N  | Mode 8b/10b Link Layer Operation                                 | .258 |

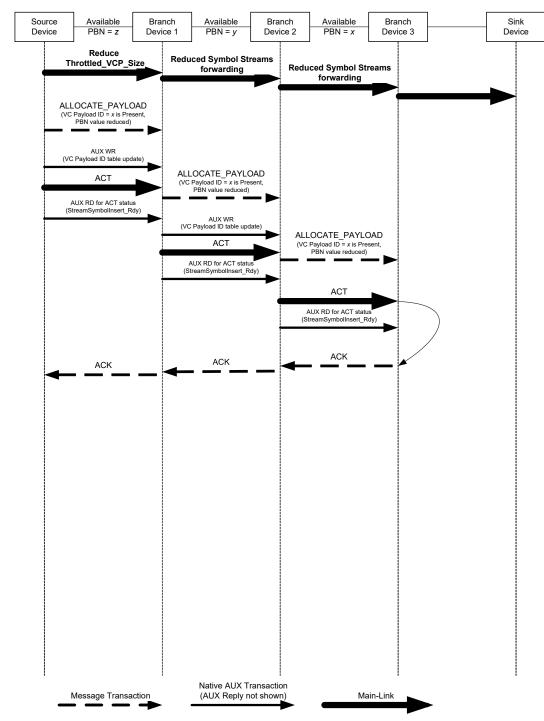

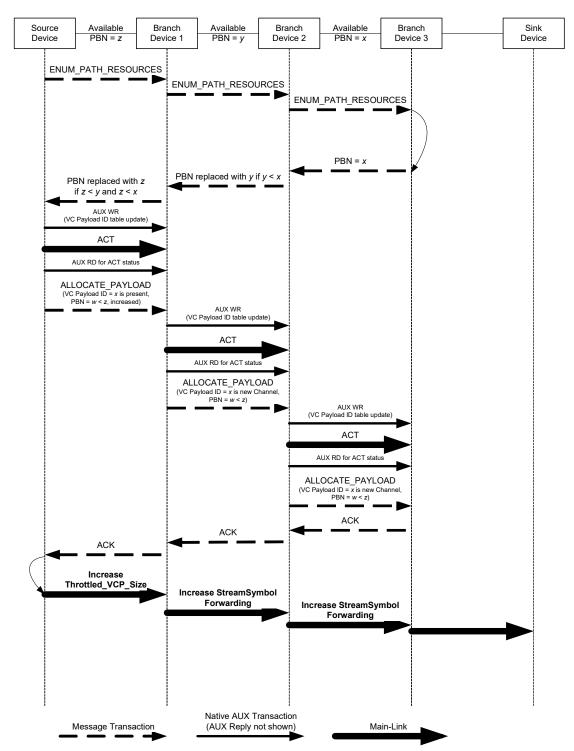

|     | 2.6.1  | Path Constraint Enumeration                                      | .263 |

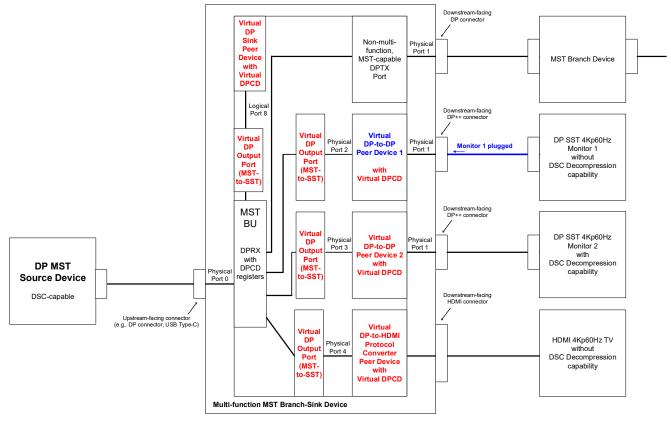

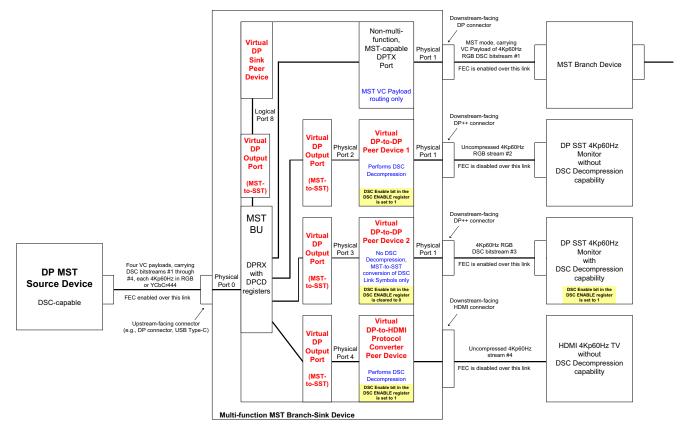

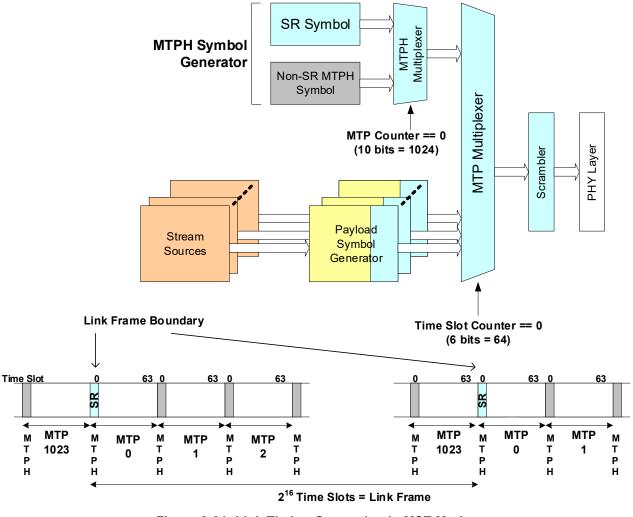

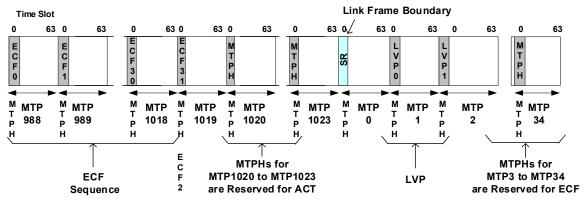

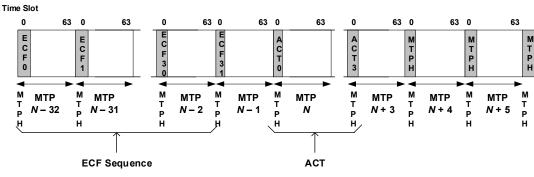

|     | 2.6.2  | Link Timing Generation Based on MST Packet                       | .273 |

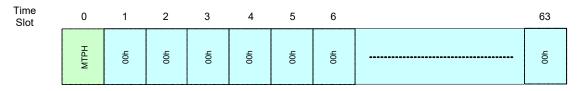

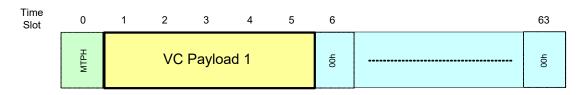

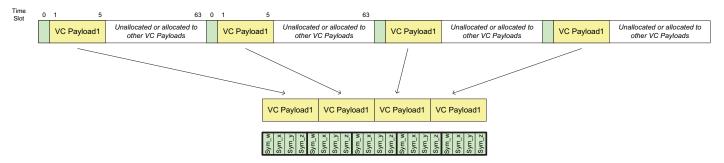

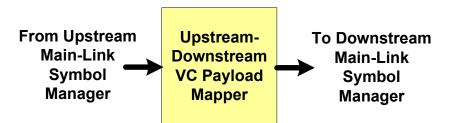

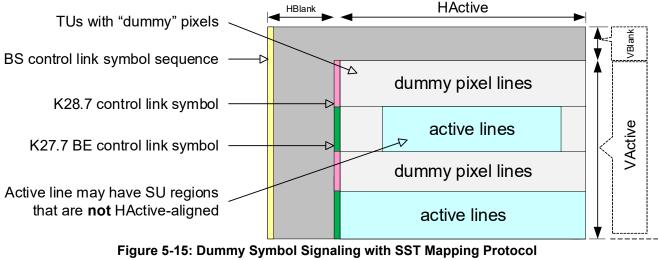

|     | 2.6.3  | Symbol Sequence Mapping into VC Payload                          | .274 |

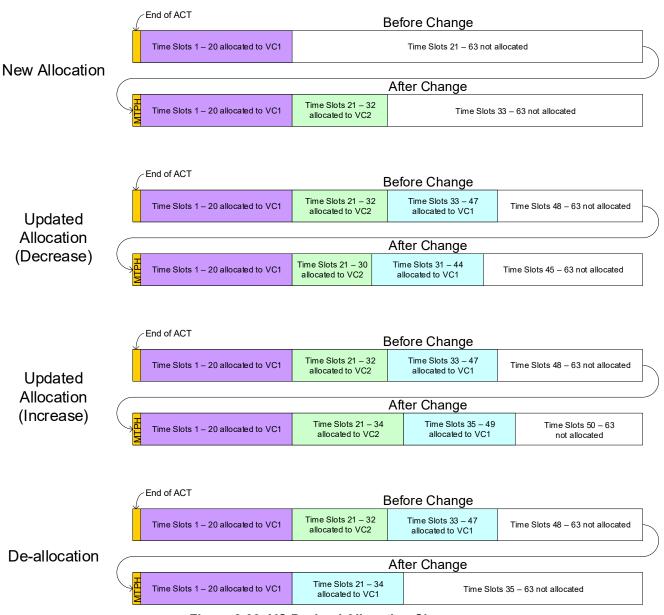

|     | 2.6.4  | Time Slot Count Allocation to VC Payload                         | .285 |

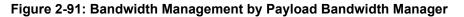

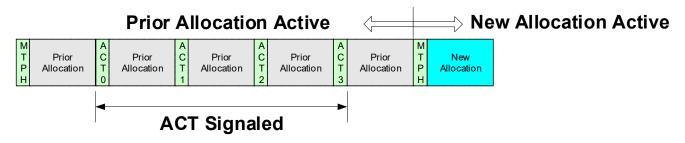

|     | 2.6.5  | VC Payload Allocation Synchronization Management                 | .294 |

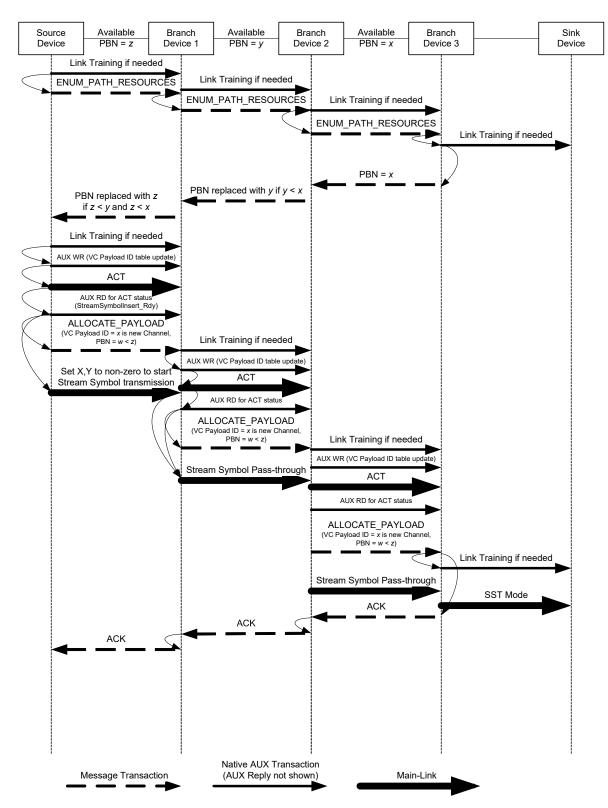

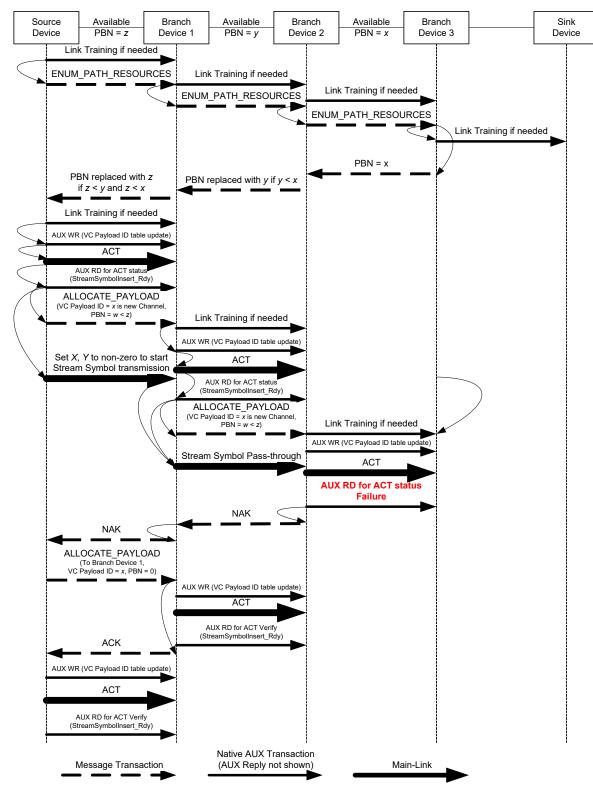

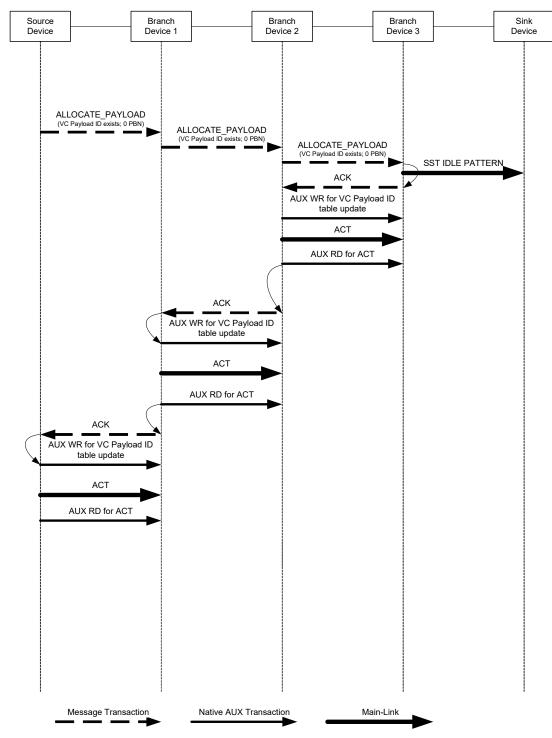

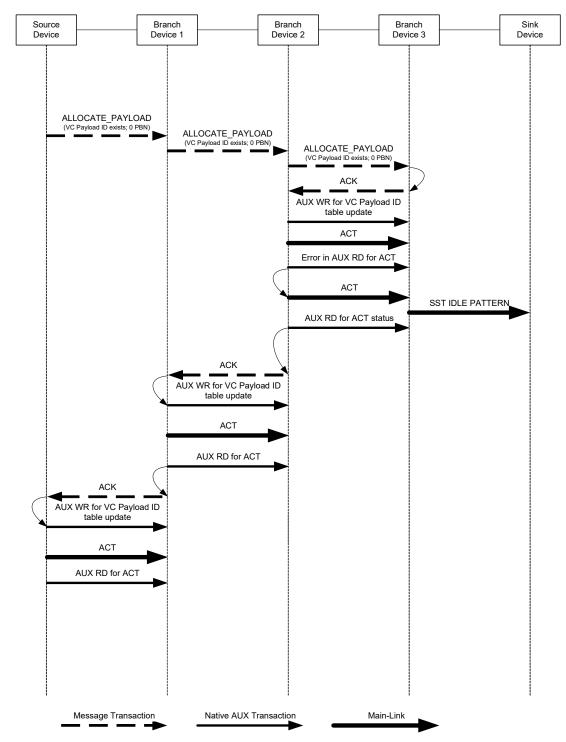

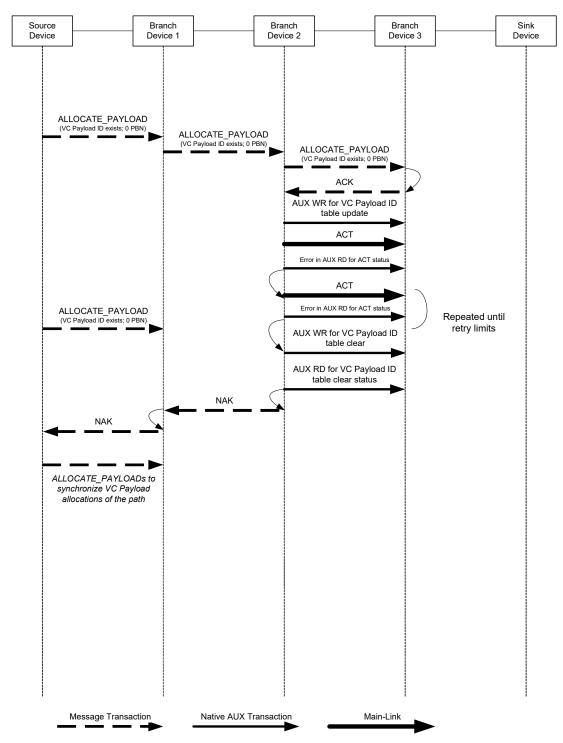

|     | 2.6.6  | ALLOCATE_PAYLOAD Timing Sequence                                 | .299 |

|     | 2.6.7  | Impacts of Various Events on VC Payload ID Table                 |      |

|     | 2.6.8  | Robustness Mandate                                               |      |

|     | 2.6.9  | Control Functions, Control Link Symbols, and K-code Assignment   | .311 |

|     | 2.6.10 |                                                                  |      |

|     | 2.6.11 | MTPH Usages for CP Extension in MST Mode                         | .315 |

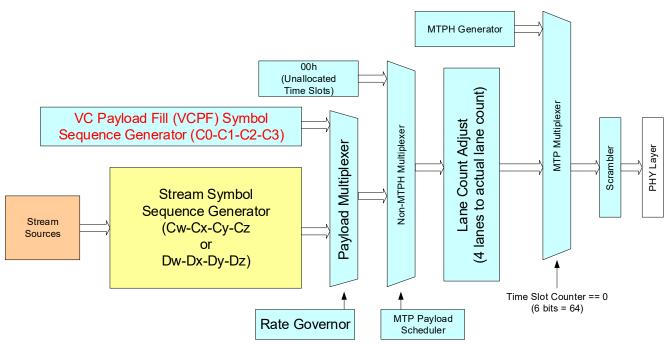

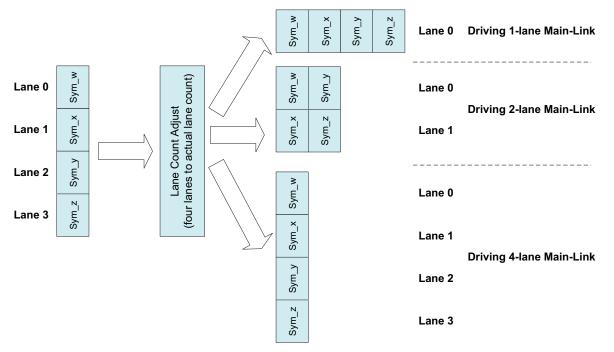

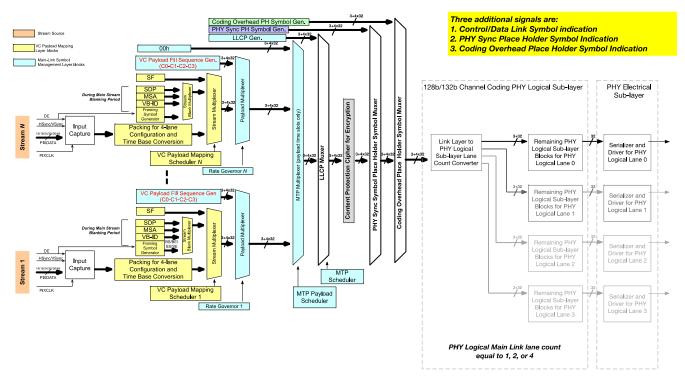

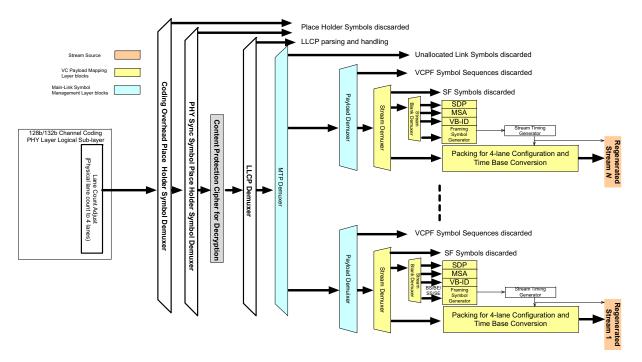

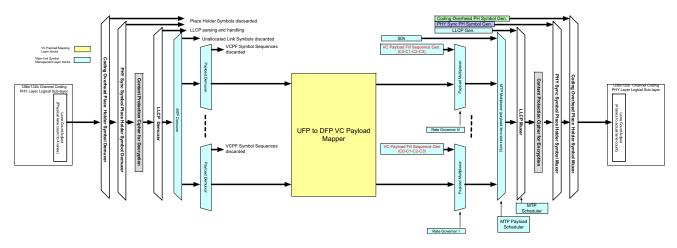

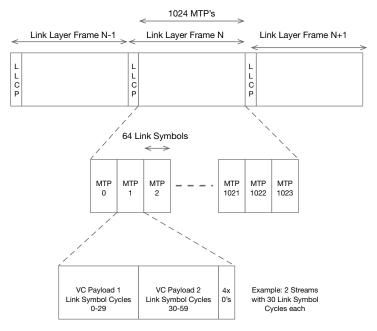

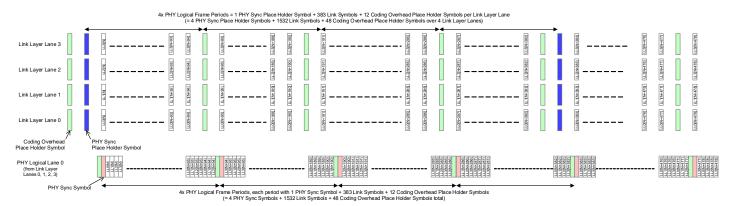

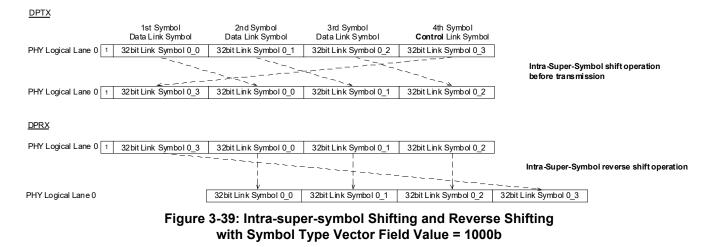

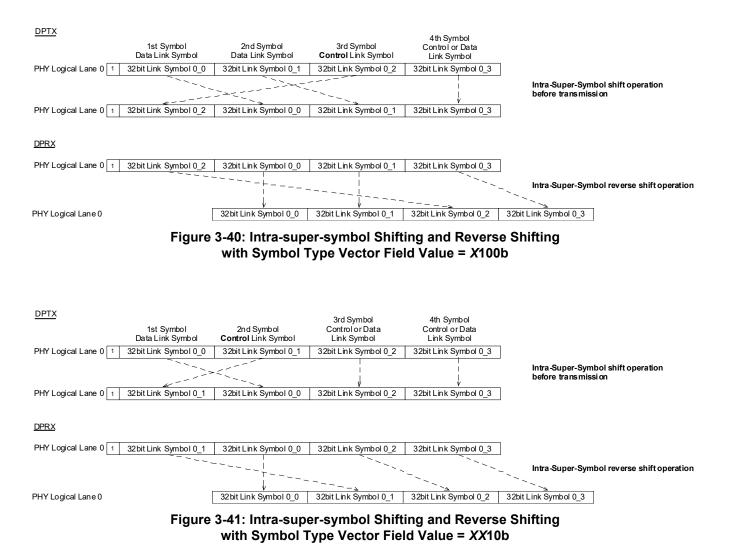

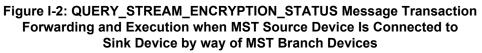

| 2.7   | Stream  | Data-to-Link Symbol Mapping with 128b/132b Link Layer                          | .317 |

|-------|---------|--------------------------------------------------------------------------------|------|

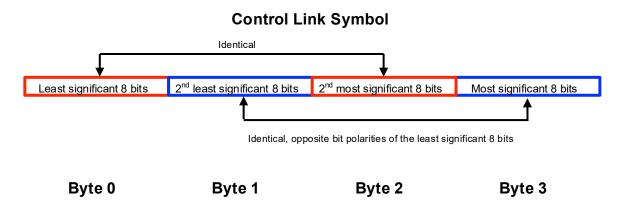

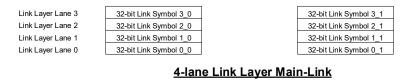

|       | 2.7.1   | 32-bit Link Symbols                                                            | .322 |

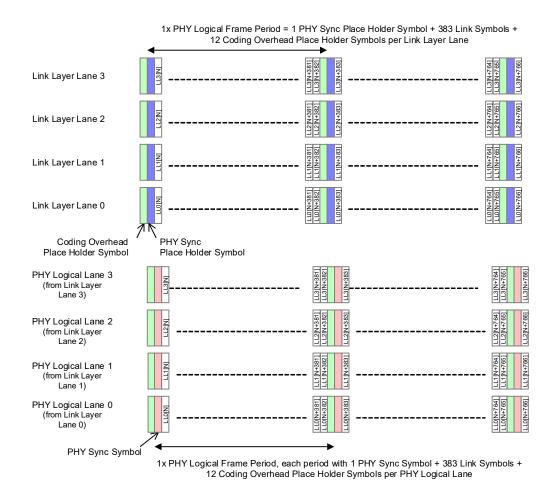

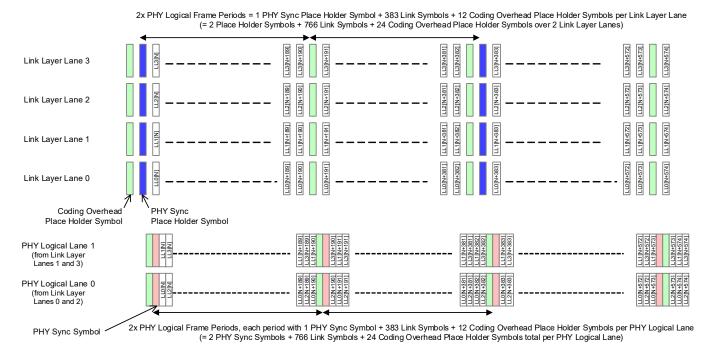

|       | 2.7.2   | Mapping to MTPs and Link Layer Frames                                          | .324 |

|       | 2.7.3   | Link Layer Control Packet                                                      | .325 |

|       | 2.7.4   | MSA Packet and VB-ID Mapping to 32-bit Link Symbols                            | .326 |

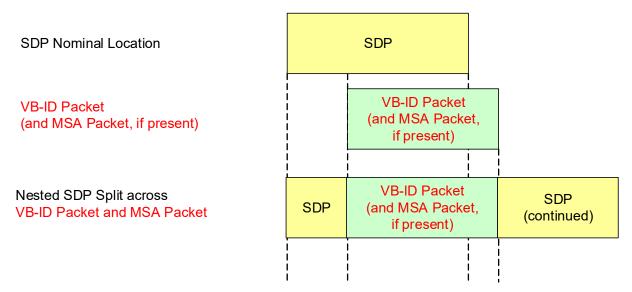

|       | 2.7.5   | SDP Mapping to 32-bit Link Symbols                                             | .328 |

|       | 2.7.6   | Time Slot Allocations                                                          | .330 |

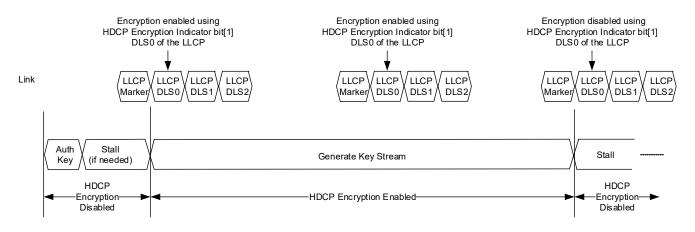

|       | 2.7.7   | 32-bit Link Symbol Content Protection                                          | .334 |

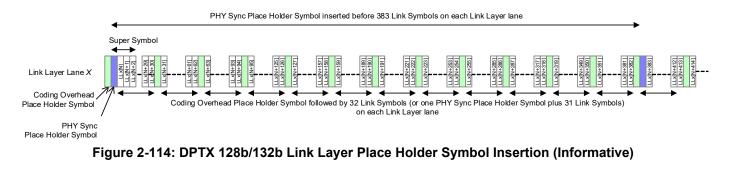

|       | 2.7.8   | Place Holder Symbol Insertion                                                  | .336 |

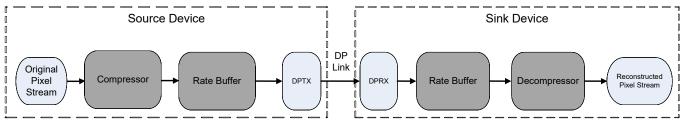

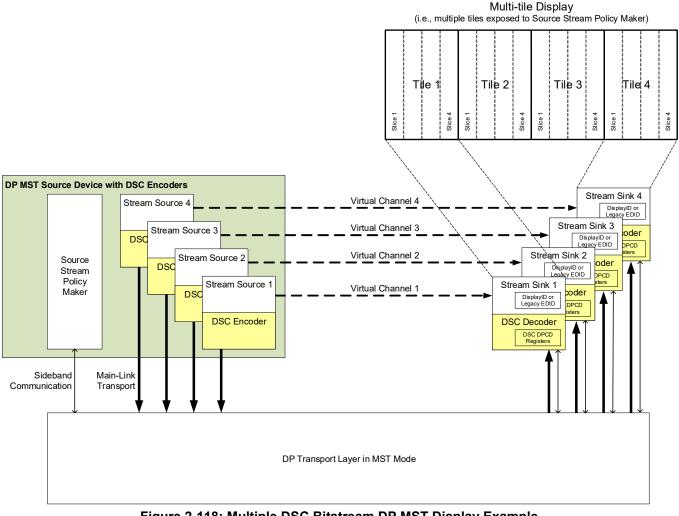

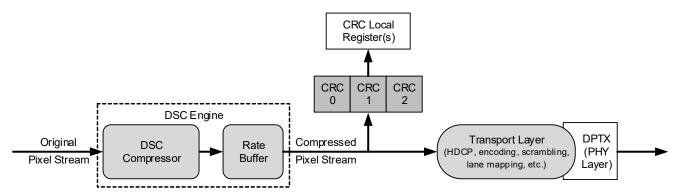

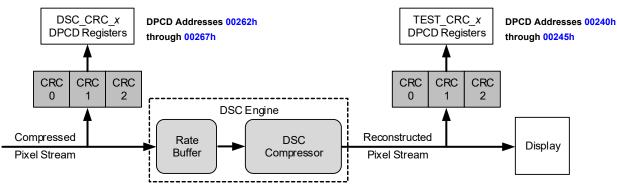

| 2.8   | Compr   | essed Display Stream Transport Services                                        | .337 |

|       | 2.8.1   | Transport Buffer Model                                                         | .337 |

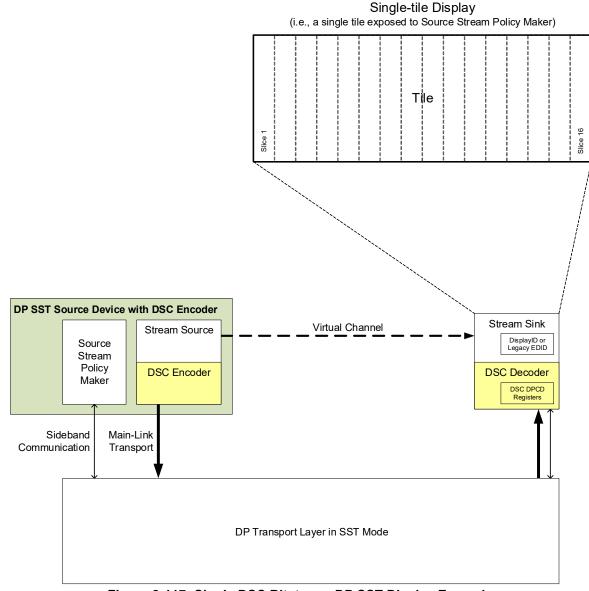

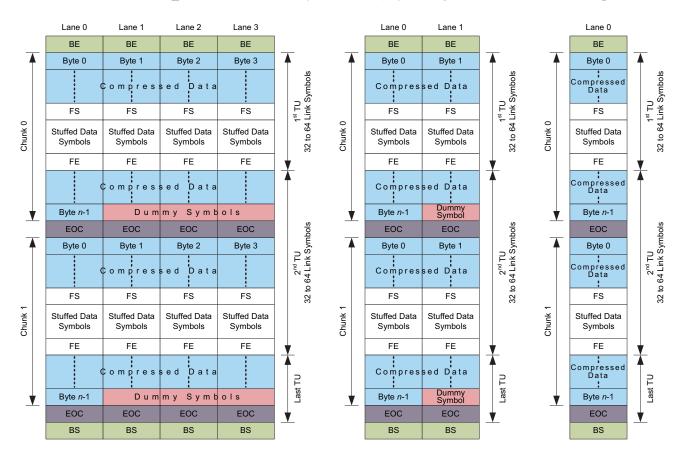

|       | 2.8.2   | DSC Bitstream Transport over DP SST/MST Link                                   | .338 |

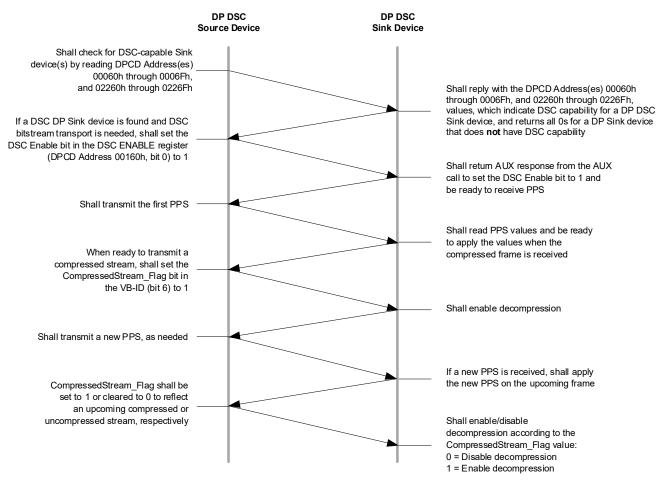

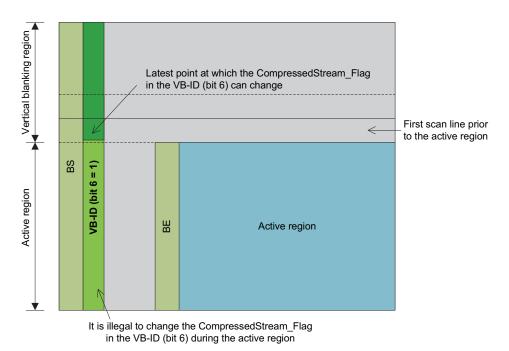

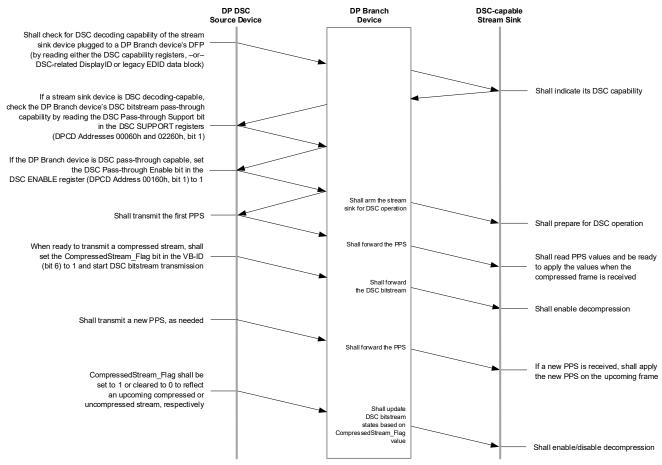

|       | 2.8.3   | DSC Configuration – Discovery, Enabling, and Disabling                         | .340 |

|       | 2.8.4   | Minimum Slices/Display Line Mandate                                            | .347 |

|       | 2.8.5   | CRCs for DSC                                                                   | .355 |

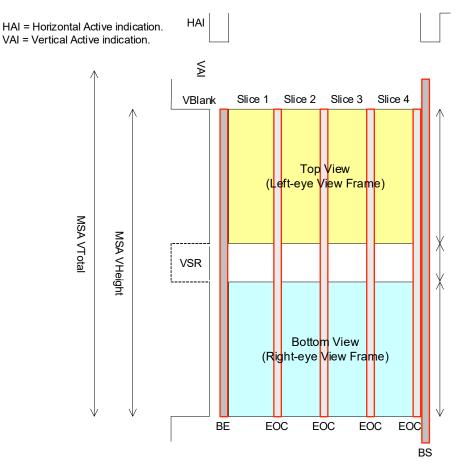

|       | 2.8.6   | DSC Bitstream Transport of 3D Stereo Video                                     | .358 |

|       | 2.8.7   | DSC Bitstream Mapping to 128b/132b Link Layer Link Symbols                     | .360 |

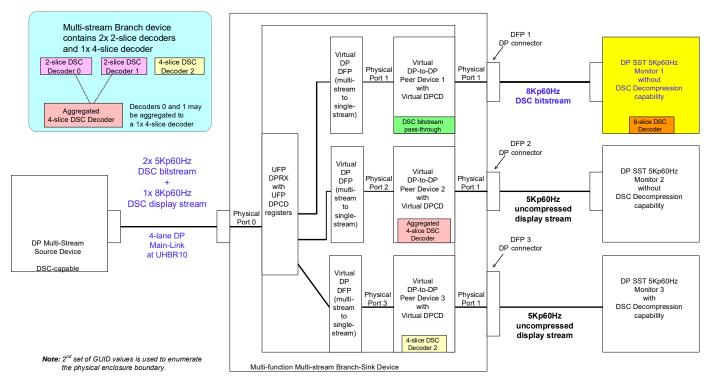

|       | 2.8.8   | DSC Bitstream Pass-through across a DP Branch Device                           | .361 |

| 2.9   | DSC S   | upport Mandate for 128b/132b Link Layer-capable DP Devices                     | .362 |

|       | 2.9.1   | DSC Support Mandates for a DP Source Device with                               |      |

|       |         | a 128b/132b Link Layer-capable DFP                                             | .363 |

|       | 2.9.2   | DSC Support Mandates for a DP Sink Device with                                 |      |

|       |         | a 128b/132b Link Layer-capable UFP                                             | .364 |

|       | 2.9.3   | DSC Support Mandates for a DP Branch Device with                               |      |

| • • • | D.C.C.C | a 128b/132b Link Layer-capable UFP                                             | .365 |

| 2.10  |         | apability, DSC Extended Capability, DSC Configuration,                         | 200  |

|       |         | P Capability Extension DPCD Registers                                          |      |

|       |         | DSC Capability and DSC Extended Capability DPCD Registers                      |      |

|       |         | DSC CONFIGURATION DPCD Register                                                |      |

|       |         | DFP Capability Extension DPCD Registers                                        |      |

| 0.11  |         | DP Branch Device DSC Decoder Configuration Examples                            |      |

| 2.11  |         | Fransaction Syntax in Manchester Transaction Format.         Common Definition |      |

|       |         | Command Definition.                                                            |      |

|       | 2.11.2  | AUX Transaction Response/Reply Timeouts                                        |      |

|       |         | Native AUX Request Transaction Syntax                                          |      |

|       |         | Native AUX Reply Transaction Syntax                                            |      |

|       |         | I <sup>2</sup> C Bus Transaction Mapping onto AUX Syntax                       |      |

|       |         | Conversion of $I^2C$ Transaction to Native AUX Transaction (Informative).      |      |

| 2.12  |         | I <sup>2</sup> C-over-AUX Transaction Clarifications and Implementation Rules  |      |

| 2.12  |         | Services                                                                       |      |

|       | 2.12.1  | 1 1                                                                            |      |

|       | 2.12.2  | Stream Transport Termination Sequence                                          |      |

|       |         | DPCD Field Address Mapping                                                     |      |

|       |         |                                                                                |      |

|       | 2.12.3  | AUX Device Services                                                            | .005 |

|           | 2.13 | Alternate Scrambler Reset for eDP                                        |     |

|-----------|------|--------------------------------------------------------------------------|-----|

|           |      | 2.13.1 Protocol Differentiation Method                                   | 606 |

|           |      | 2.13.2 Symbol Error Rate Measurement Pattern Output (Informative)        | 606 |

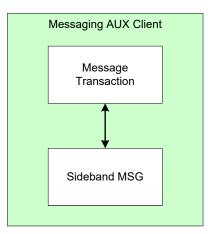

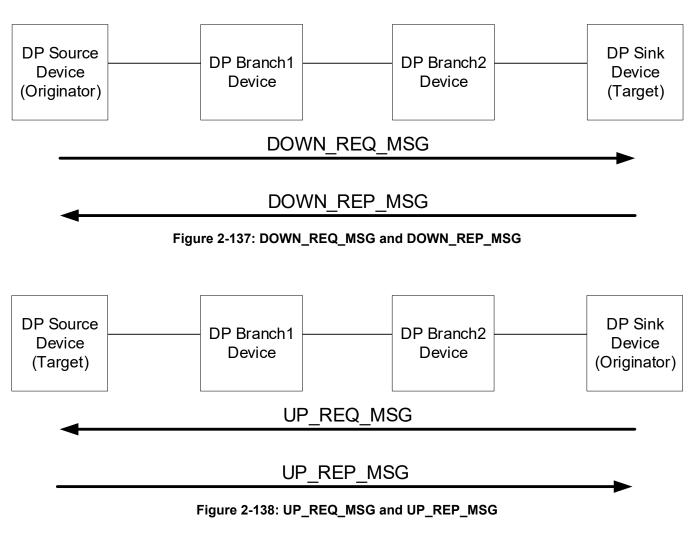

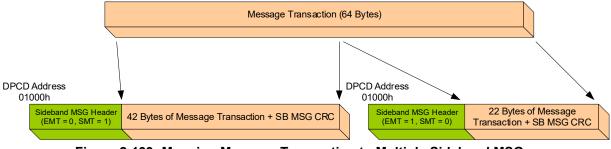

|           | 2.14 | Messaging AUX Client                                                     |     |

|           |      | 2.14.1 Messaging AUX Client Layers                                       |     |

|           |      | 2.14.2 Message Transaction Layer.                                        | 612 |

|           |      | 2.14.3 Sideband MSG Layer                                                |     |

|           |      | 2.14.4 AUX Support for Messaging AUX Client                              | 628 |

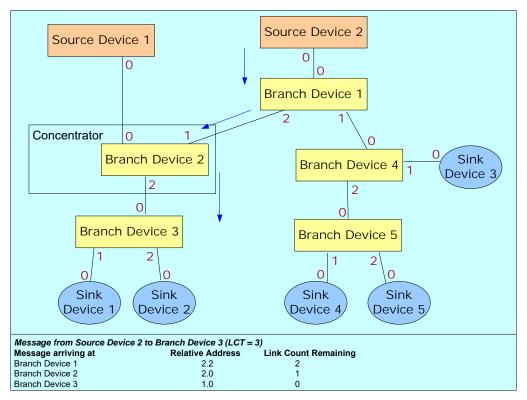

|           |      | 2.14.5 RAD Updated by MST Devices in the Path                            | 631 |

|           |      | 2.14.6 Broadcast Message Transactions                                    |     |

|           |      | 2.14.7 Message Delivery                                                  | 633 |

|           |      | 2.14.8 Error Handling                                                    | 638 |

|           |      | 2.14.9 Descriptions of Available Message Transaction Requests            | 641 |

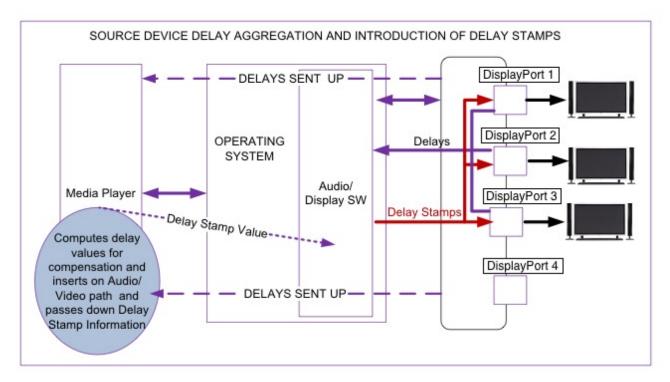

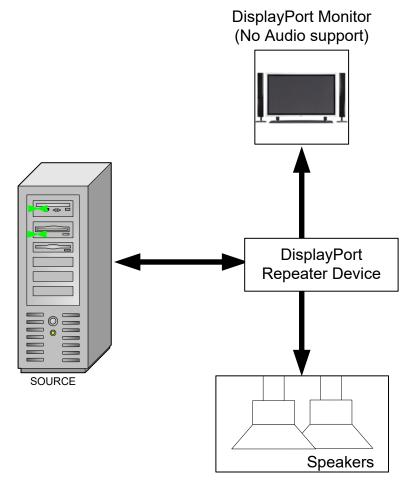

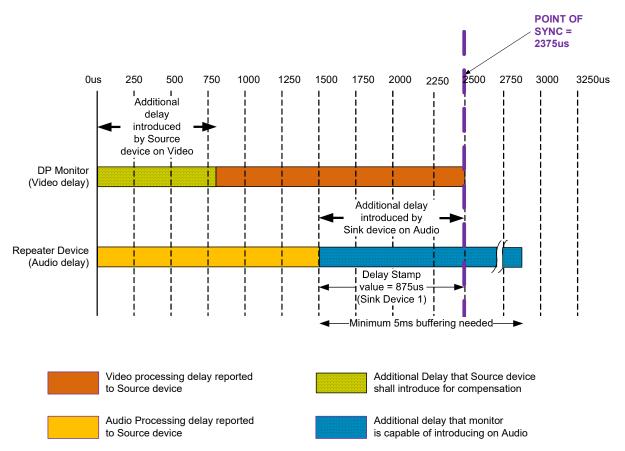

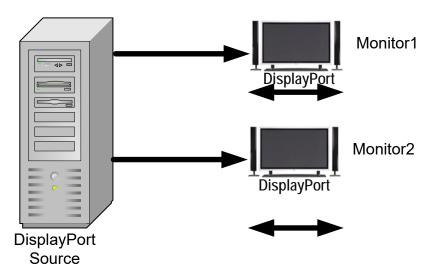

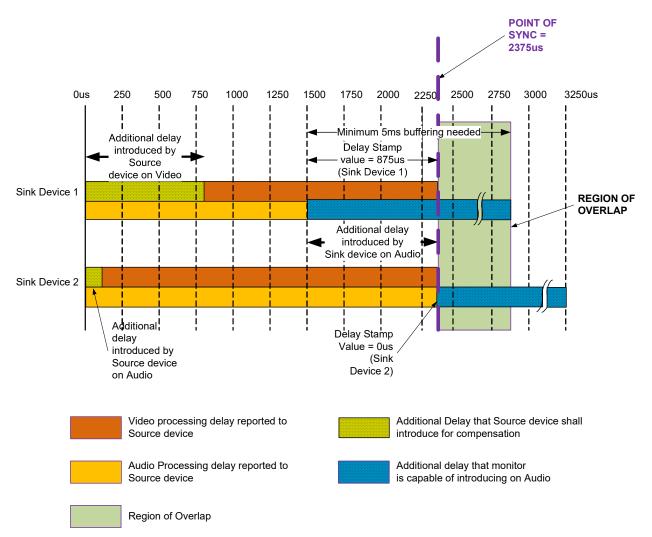

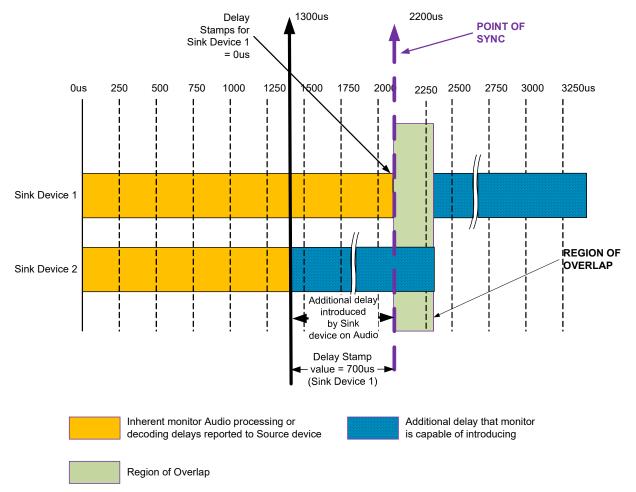

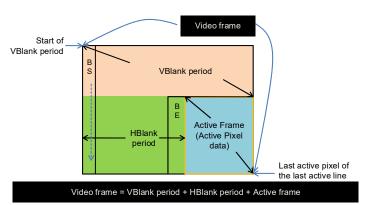

|           | 2.15 | Audio-to-video and Audio-to-audio Synchronization                        | 662 |

|           |      | 2.15.1 Overview                                                          | 662 |

|           |      | 2.15.2 DP AV Sync Data Block                                             | 663 |

|           |      | 2.15.3 Delay Compensation                                                | 664 |

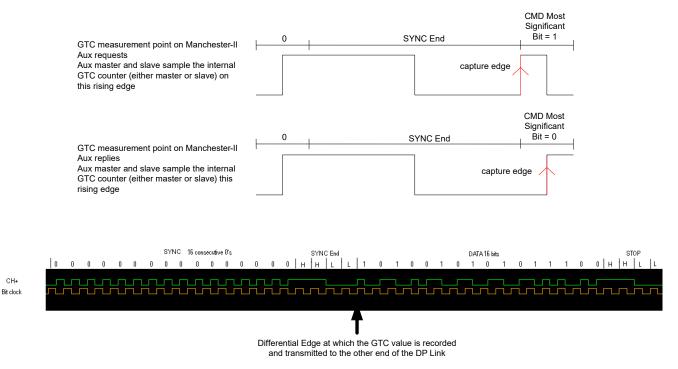

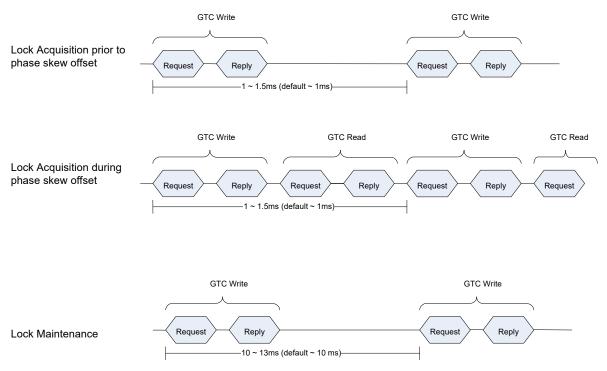

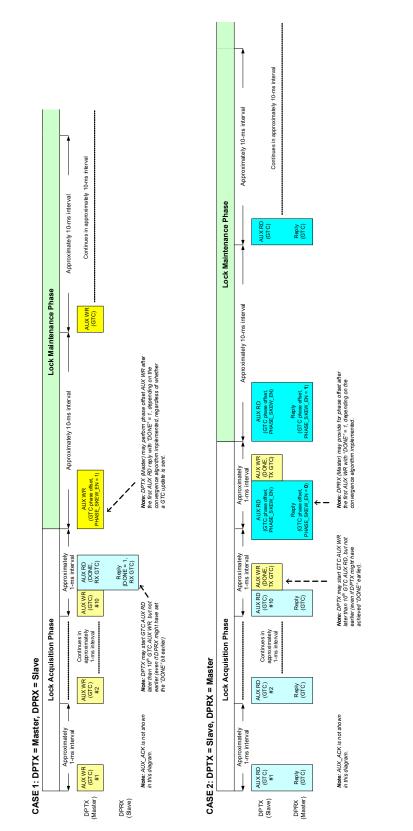

|           | 2.16 | GTC and Audio Inter-channel Sync                                         | 671 |

|           |      | 2.16.1 GTC                                                               | 671 |

|           |      | 2.16.2 Application of GTC for Audio Inter-channel Synchronization        | 685 |

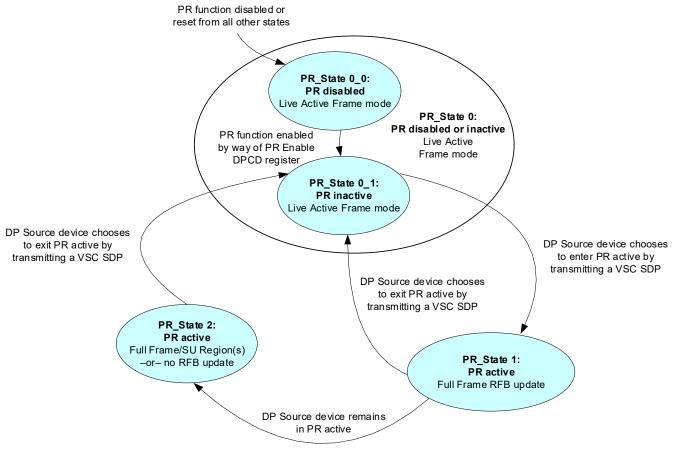

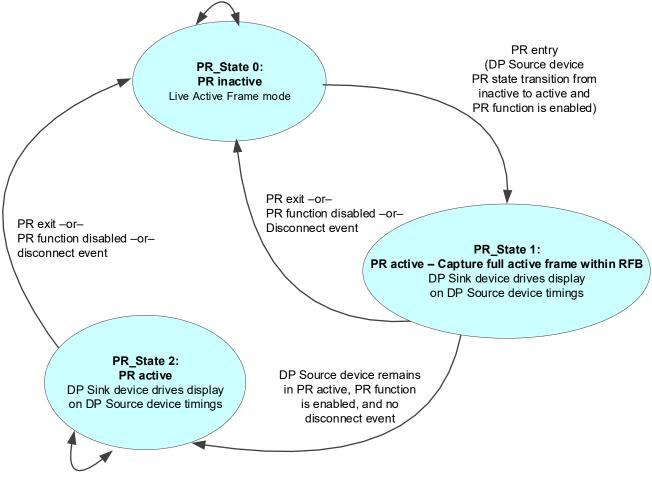

|           | 2.17 | Panel Replay Mode                                                        | 687 |

|           |      | 2.17.1 Comparison to Panel Self Refresh Mode                             | 687 |

|           |      | 2.17.2 Applicability of Panel Replay Mode                                | 688 |

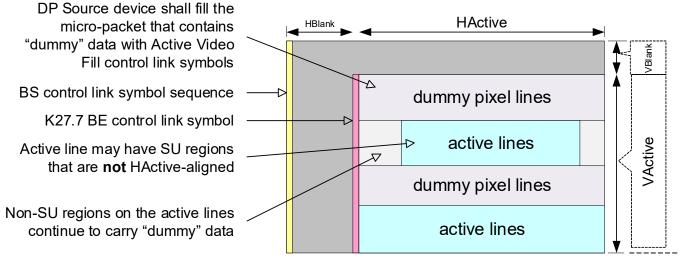

|           |      | 2.17.3 Video Timing, HDCP, and Audio Streaming in Panel Replay Mode      | 689 |

|           |      | 2.17.4 Panel Replay Mode Enumeration and Configuration                   | 690 |

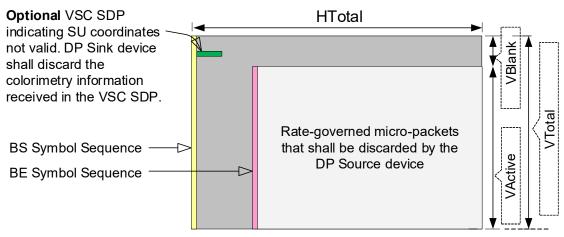

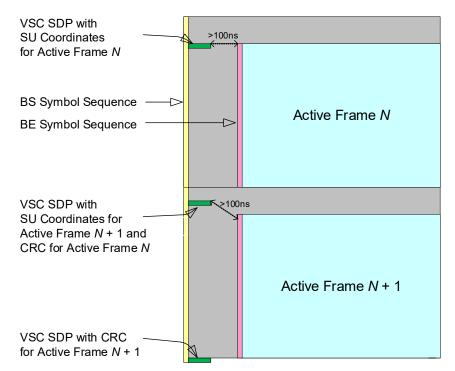

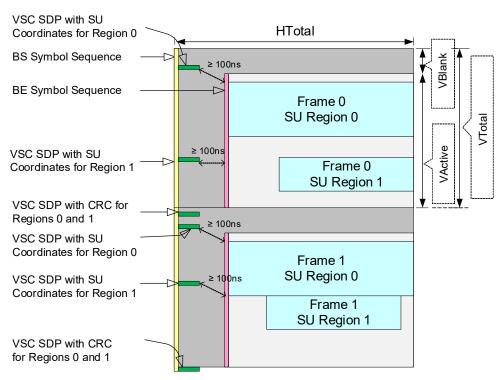

|           |      | 2.17.5 VSC SDP Use for Panel Replay                                      | 691 |

|           |      | 2.17.6 Transition between Live Active Frame and Panel Replay Modes       | 694 |

|           |      | 2.17.7 Panel Replay with no Live Active Frame Update                     | 697 |

|           |      | 2.17.8 Full-screen Live Active Frame Update in Panel Replay Mode         | 698 |

|           |      | 2.17.9 Selective Update in Panel Replay Mode                             | 699 |

|           |      | 2.17.10 Data Integrity and RFB Storage Error Check and Corrective Action | 700 |

|           |      | 2.17.11 DPCD Registers Used for Panel Replay                             |     |

| Section 3 | РНҮ  | Layer Specifications                                                     |     |

|           | 3.1  | Introduction                                                             |     |

|           | _    | 3.1.1 PHY Layer Functions                                                |     |

|           |      | 3.1.2 Link-PHY Layer Interface Signals                                   |     |

|           |      | 3.1.3 PHY Layer and Link Media Interface Signals                         |     |

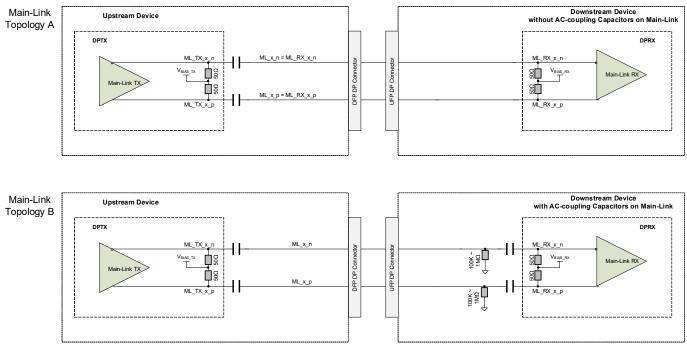

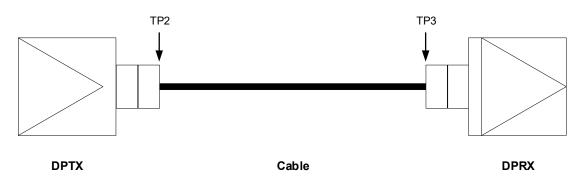

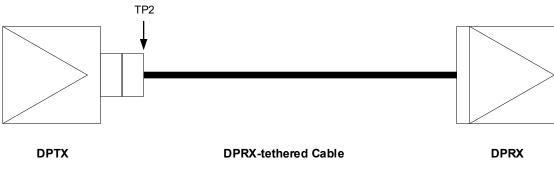

|           |      | 3.1.4 Main-Link Compliance Configurations                                |     |

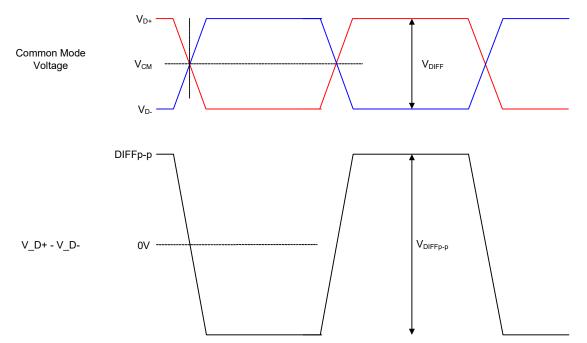

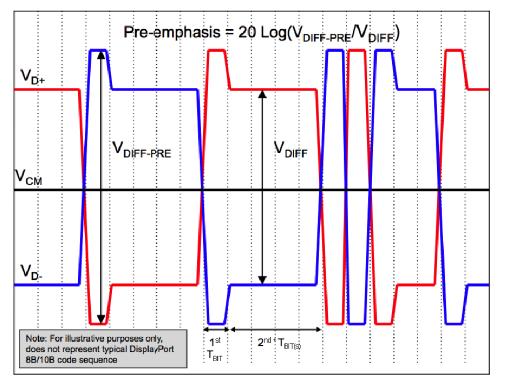

|           |      | 3.1.5 Electrical Signal Definitions                                      |     |

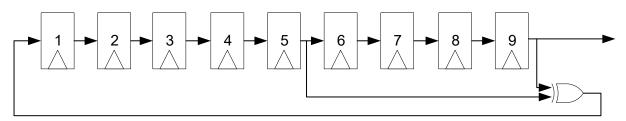

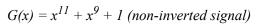

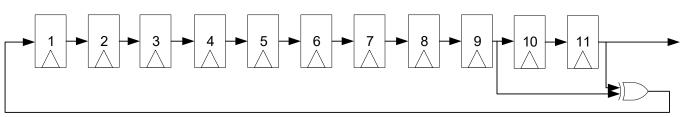

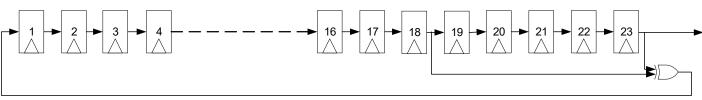

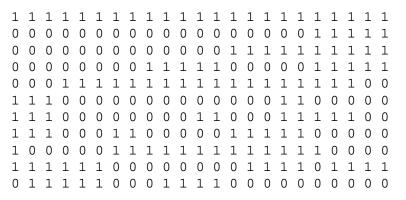

|           |      | 3.1.6 8b/10b Scrambling                                                  |     |

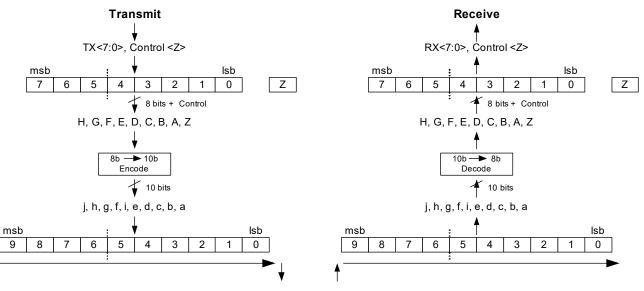

|           |      | 3.1.7 8b/10b Symbol Coding and Serialization/De-serialization.           |     |

|           |      |                                                                          |     |

| 3.2  | DP_PV     | VR for Box-to-Box DP Connection                                   | 713  |

|------|-----------|-------------------------------------------------------------------|------|

|      | 3.2.1     | DP_PWR User Detection Method                                      | 715  |

|      | 3.2.2     | DP_PWR Wire                                                       | 715  |

|      | 3.2.3     | Inrush Energy                                                     | 715  |

|      | 3.2.4     | Voltage Droop                                                     | 716  |

|      | 3.2.5     | Over-current Protection.                                          | 716  |

| 3.3  | Hot Plu   | ug/Unplug Detect Circuitry                                        | 717  |

| 3.4  | AUX_      | СН                                                                | 720  |

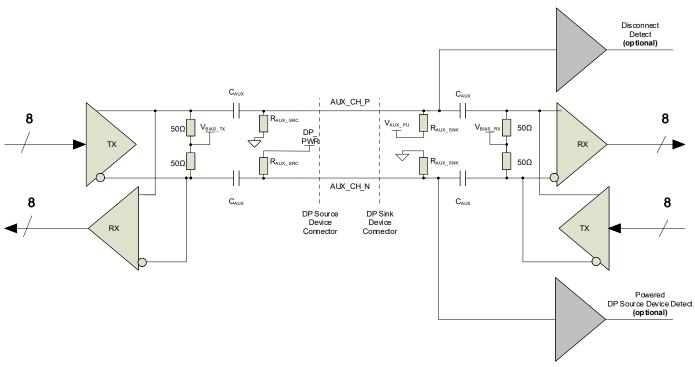

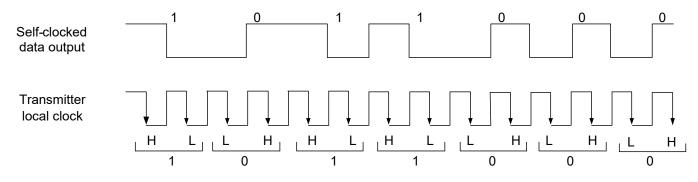

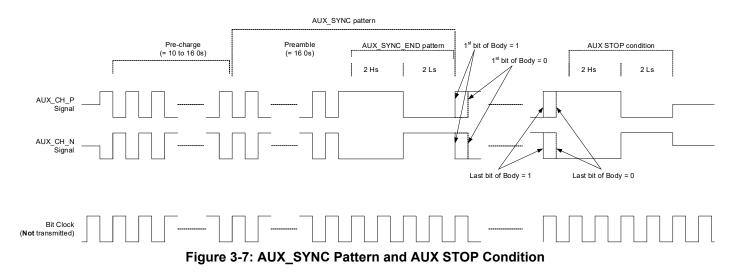

|      | 3.4.1     | AUX_CH Logical Sub-block                                          | 721  |

|      | 3.4.2     | AUX_CH Electrical Sub-block                                       | 723  |

| 3.5  | Main-L    | .ink                                                              | 731  |

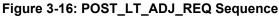

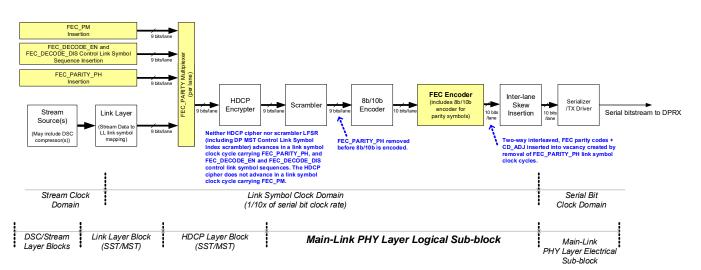

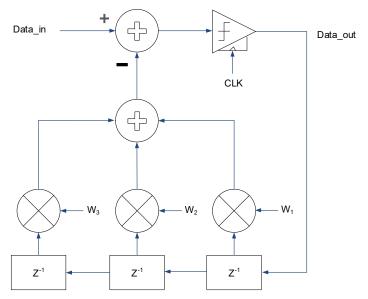

|      | 3.5.1     | Main-Link 8b/10b PHY Logical Sub-layer.                           | 731  |

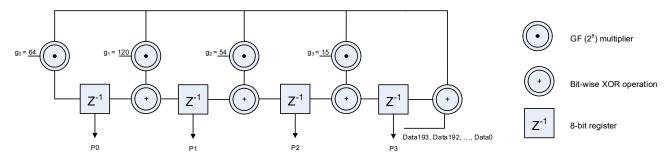

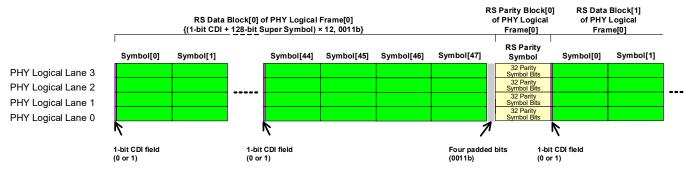

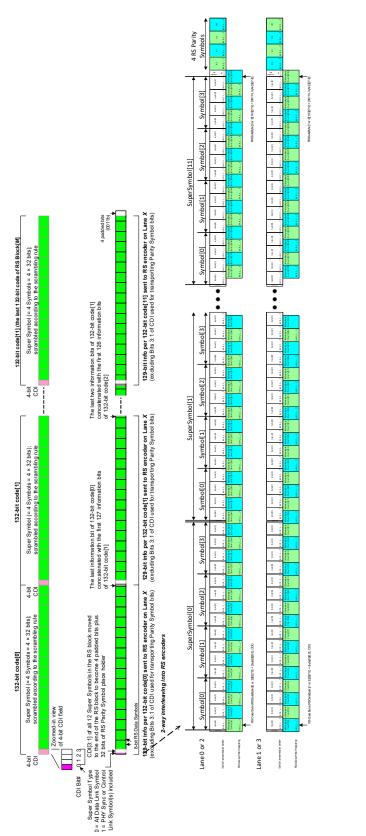

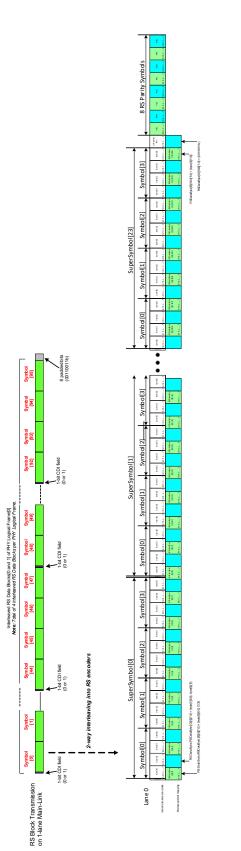

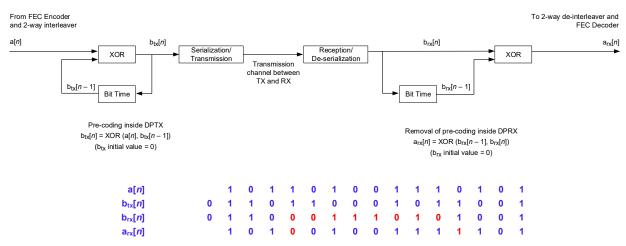

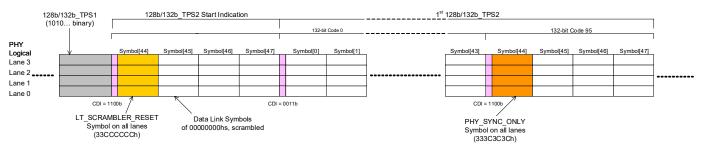

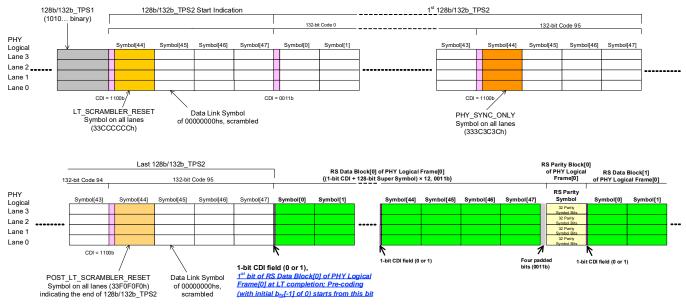

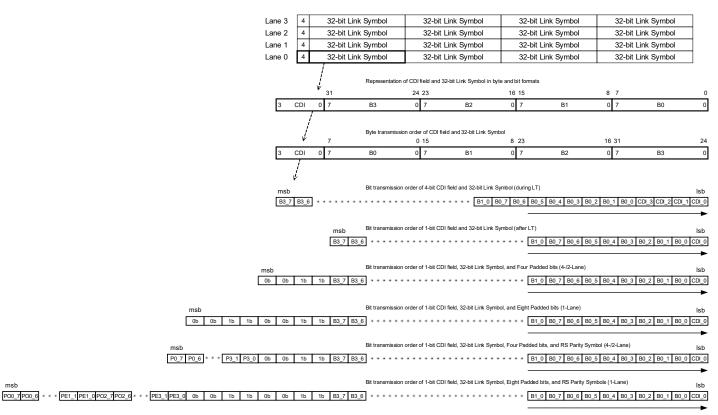

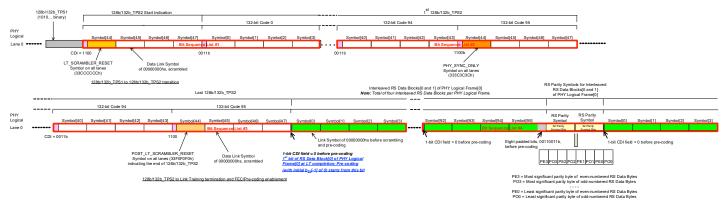

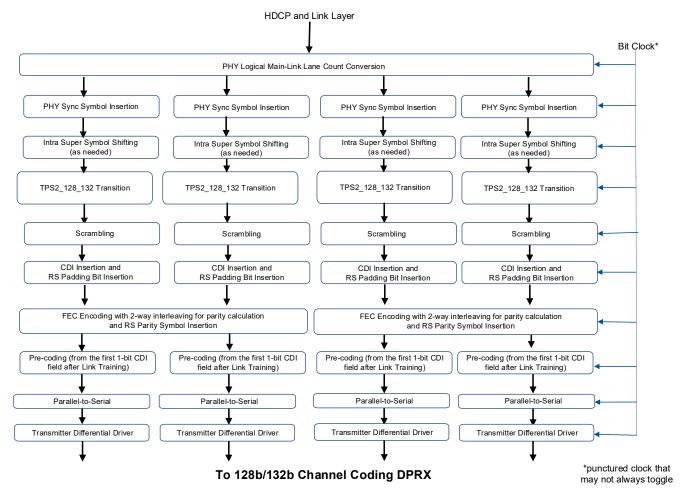

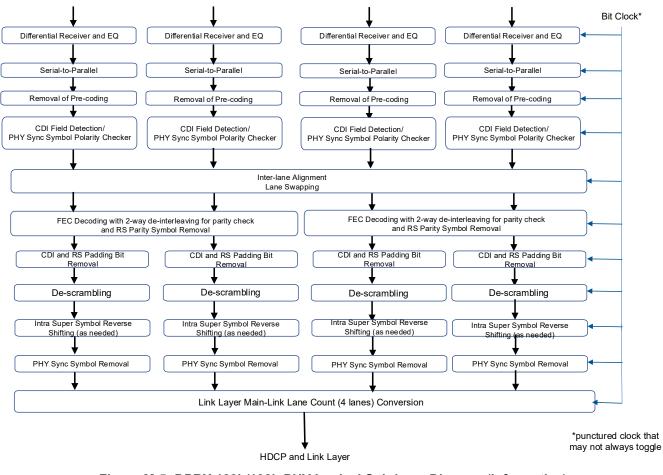

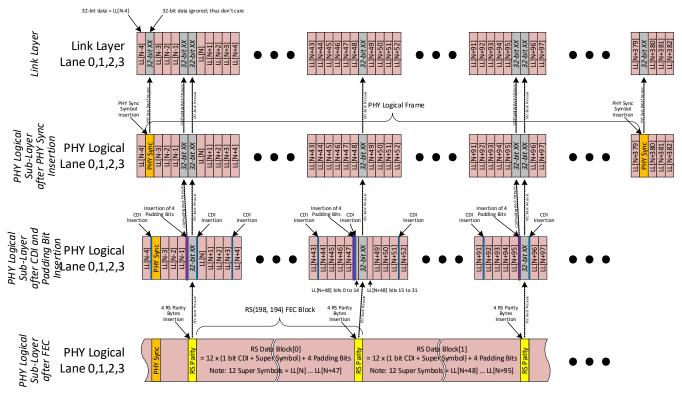

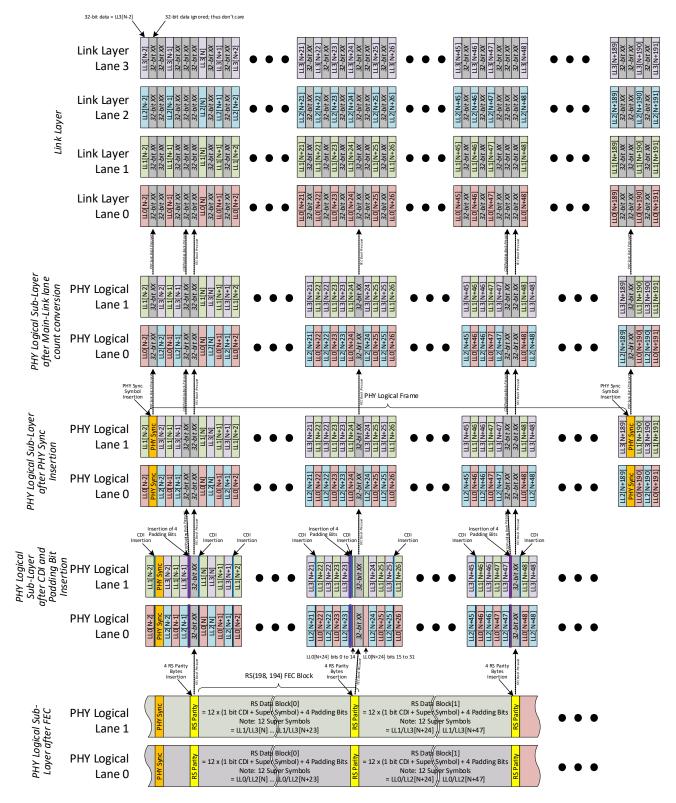

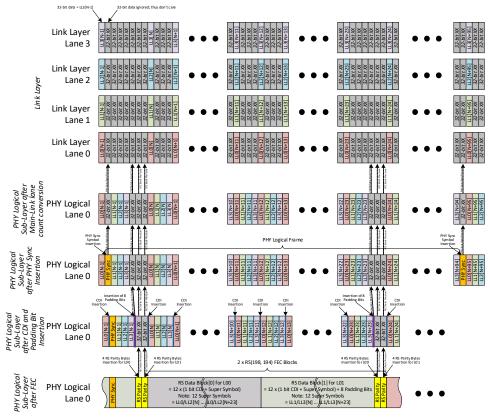

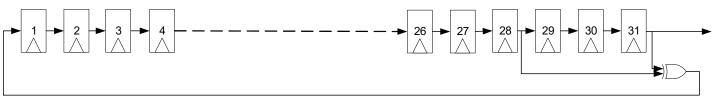

|      | 3.5.2     | Main-Link 128b/132b PHY Logical Sub-layer.                        | 772  |

|      | 3.5.3     | Main-Link PHY Logical Sublayer FEC- and PHY Test-related Register | s812 |

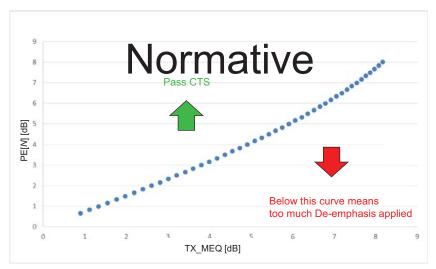

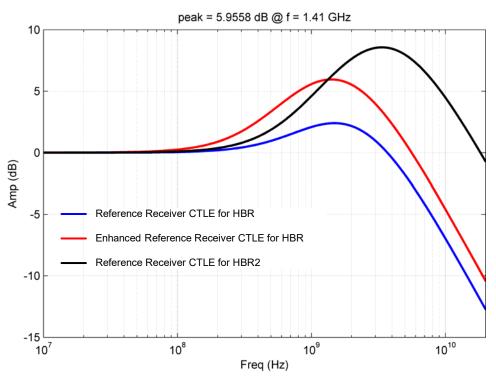

|      | 3.5.4     | 8b/10b Main-Link Electrical Sub-block                             | 822  |

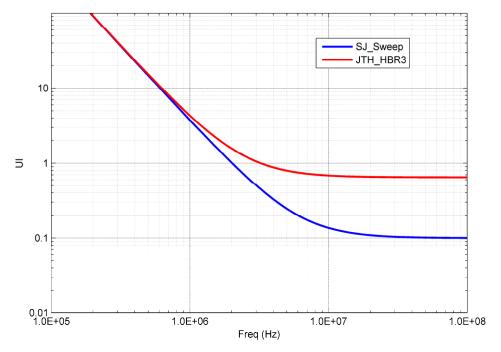

|      | 3.5.5     | 128b/132b Main-Link PHY Electrical Sub-block.                     | 852  |

|      | 3.5.6     | ESD and EOS Protection                                            |      |

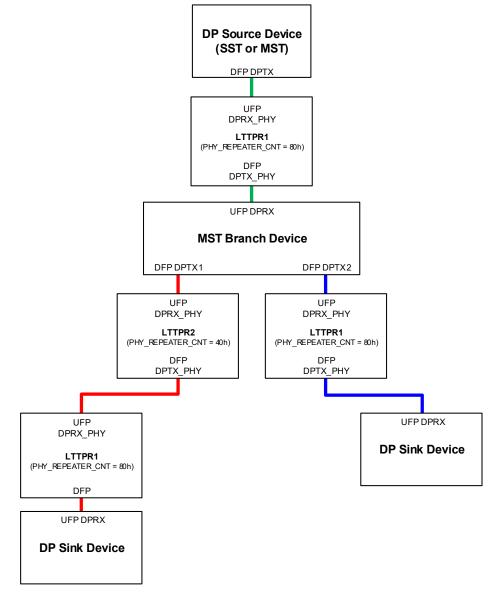

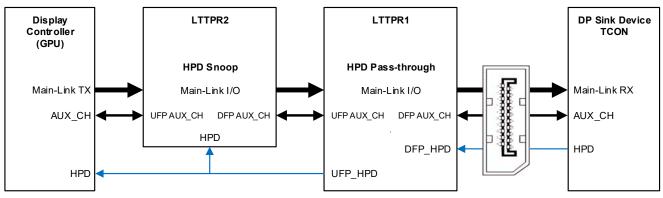

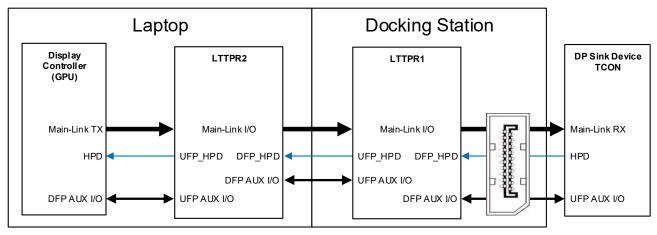

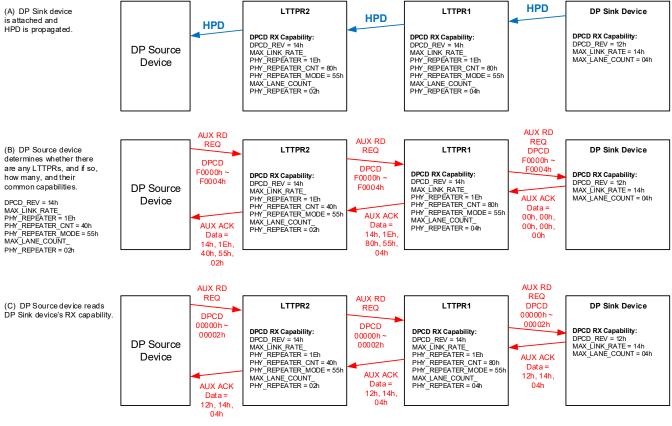

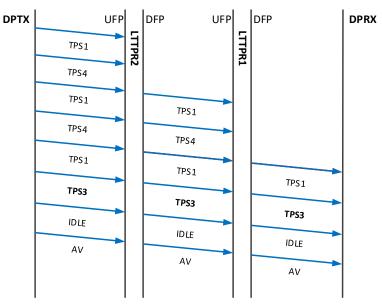

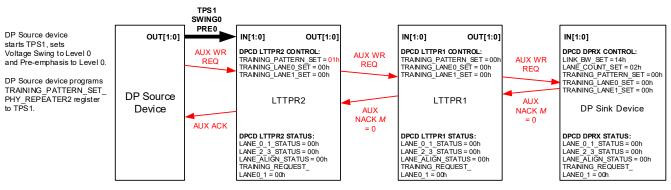

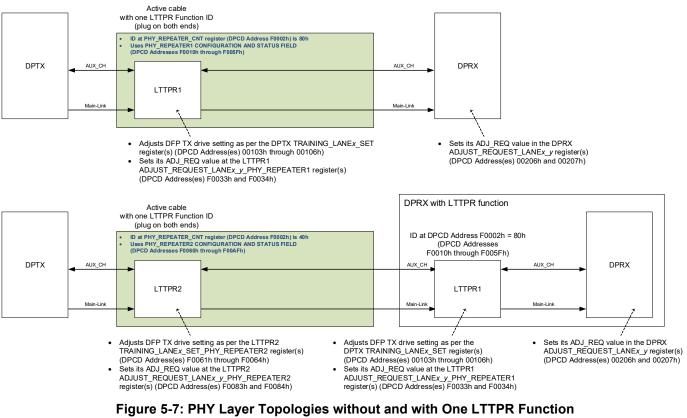

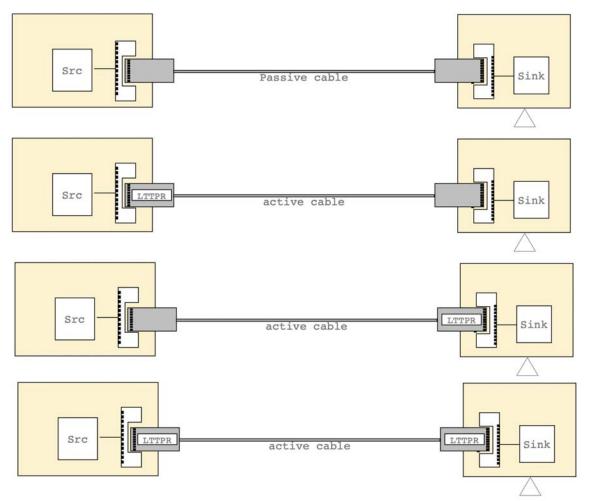

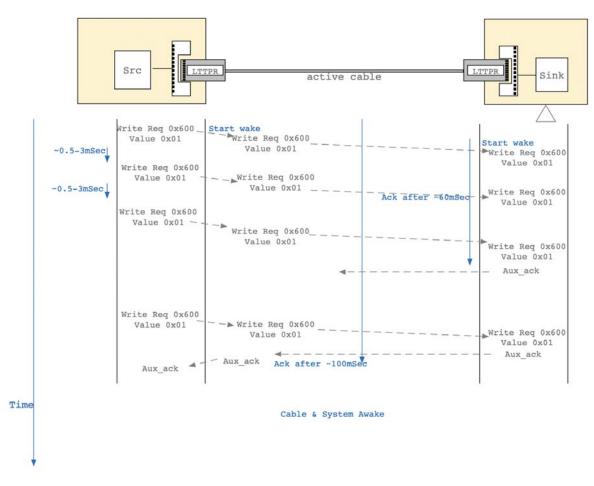

| 3.6  | LTTPR     | Rs                                                                |      |

|      | 3.6.1     | Introduction                                                      |      |

|      | 3.6.2     | Signal Routing Mandates                                           |      |

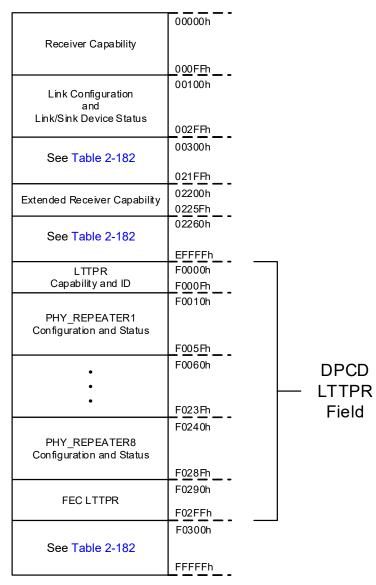

|      | 3.6.3     | LTTPR DPCD Address Mapping                                        |      |

|      | 3.6.4     | LTTPR DPCD Registers                                              |      |

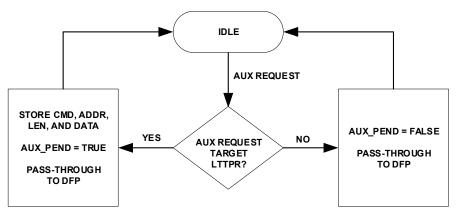

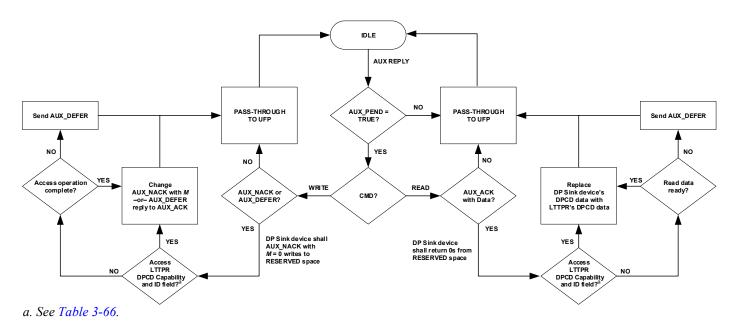

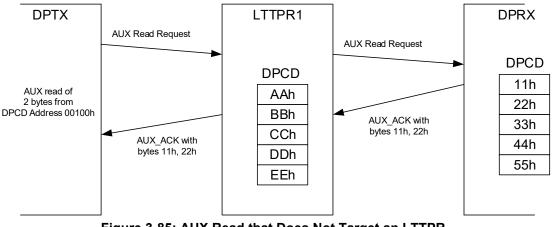

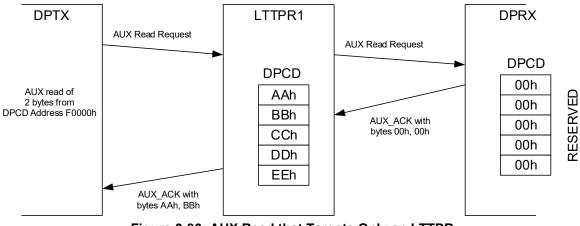

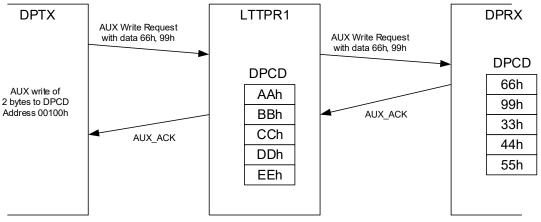

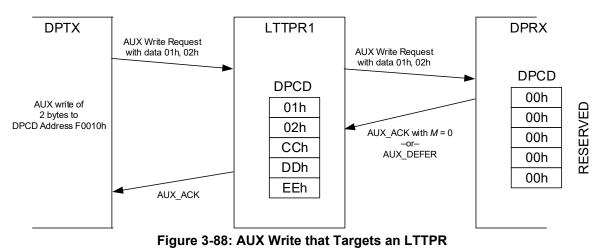

|      | 3.6.5     | AUX Transaction Handling Mandates                                 | 883  |

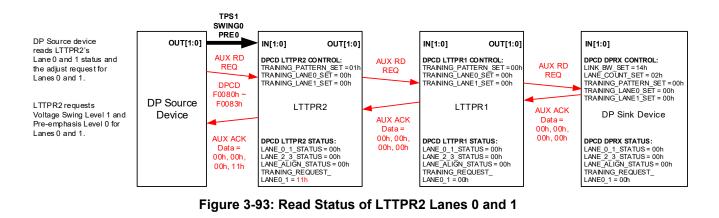

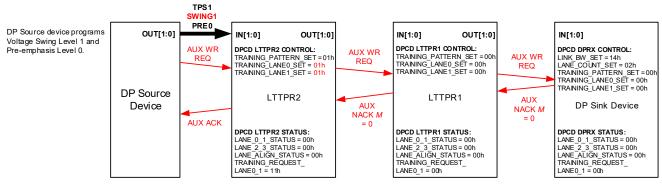

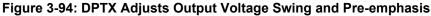

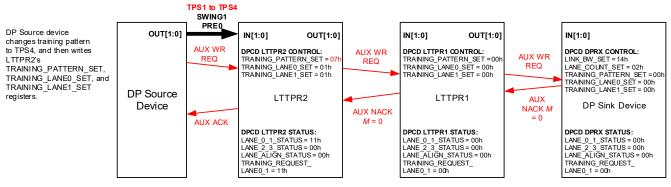

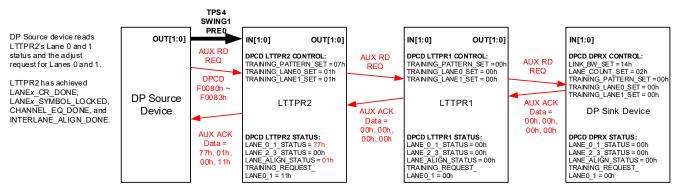

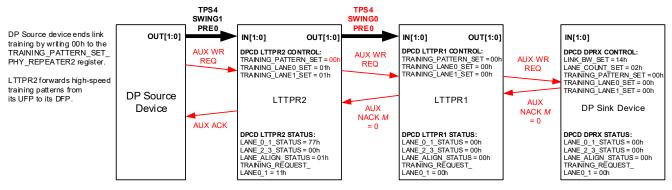

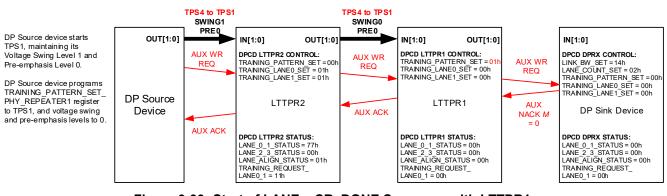

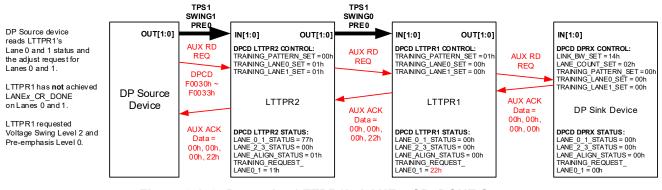

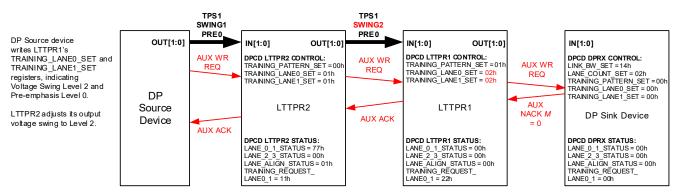

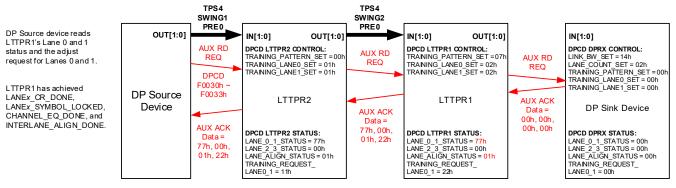

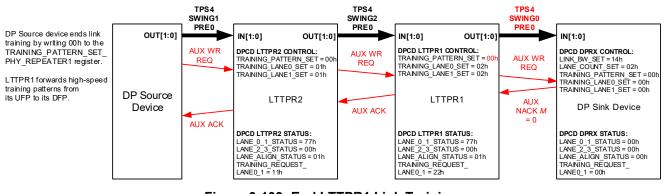

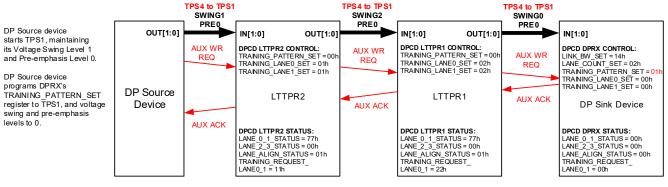

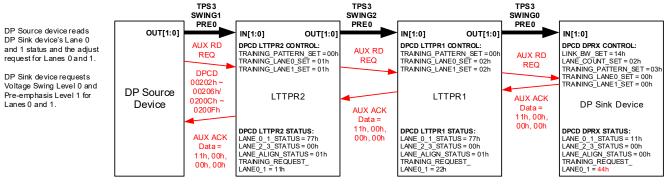

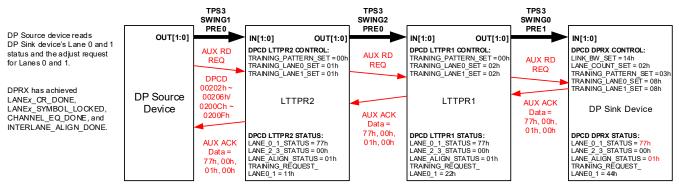

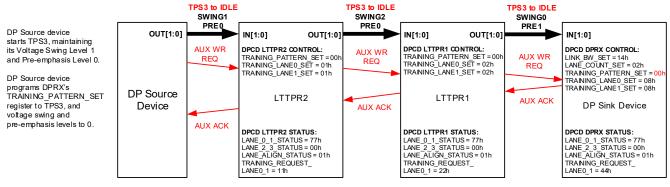

|      | 3.6.6     | Link Training                                                     | 889  |

|      | 3.6.7     | Transition to Transparent Mode                                    |      |

|      | 3.6.8     | Dual Mode Mandates                                                | 908  |

|      | 3.6.9     | LTTPR Electrical Specification Mandates                           | 908  |

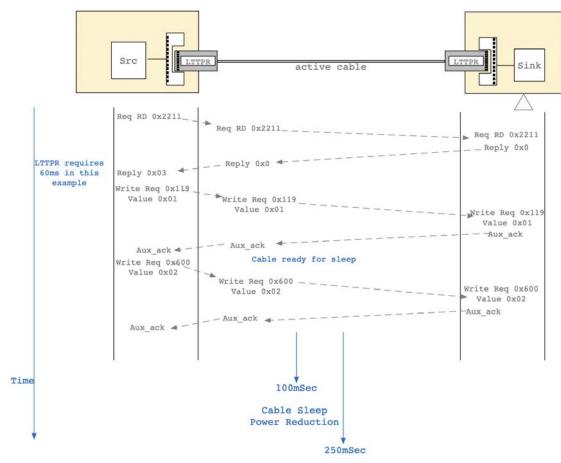

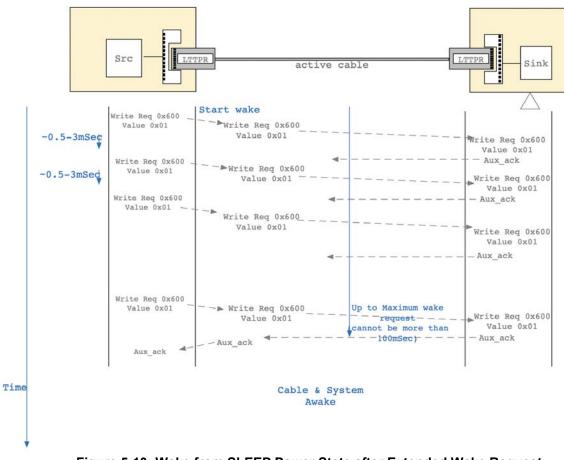

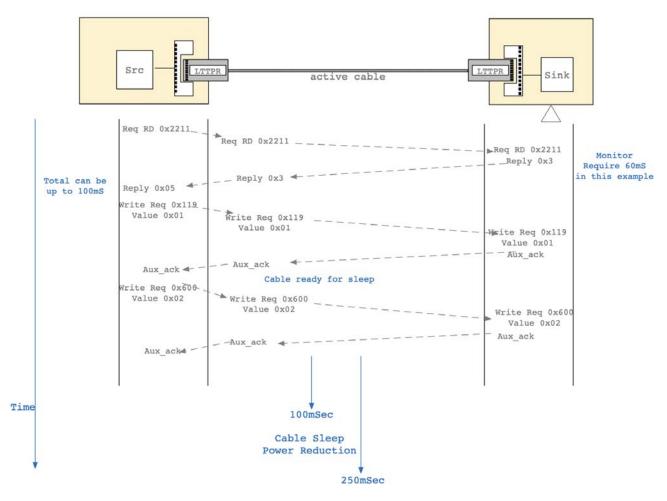

|      | 3.6.10    | LTTPR Power-saving State.                                         | 909  |

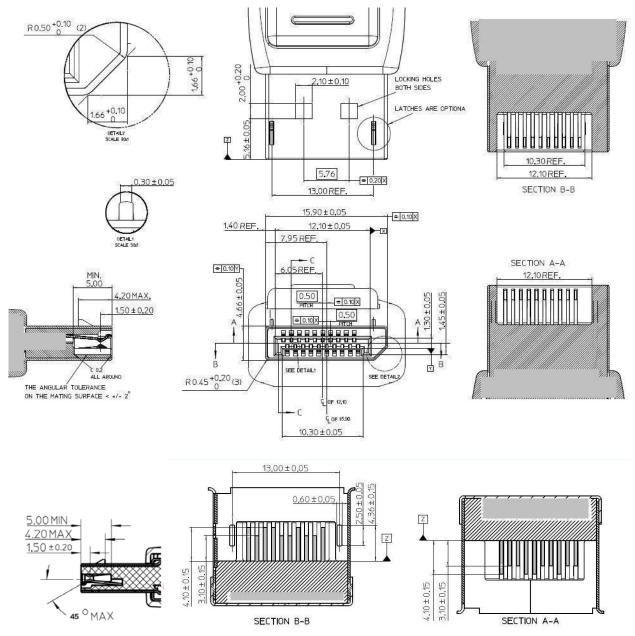

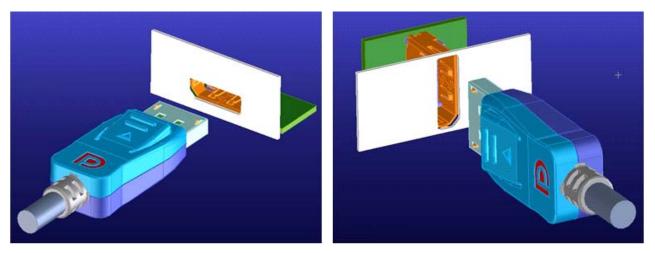

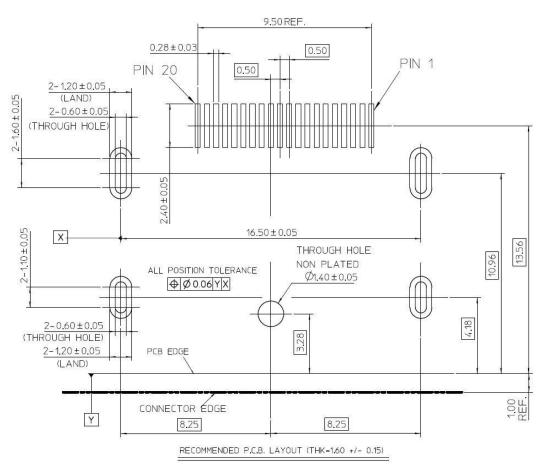

| Mech | nanical S | Specifications                                                    | 911  |

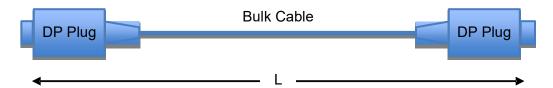

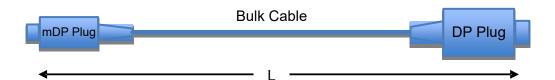

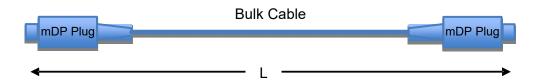

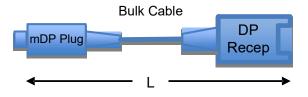

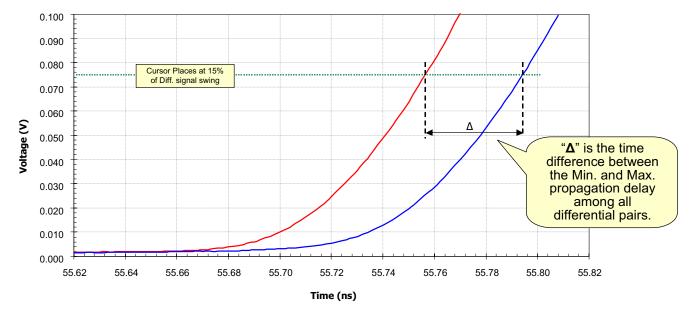

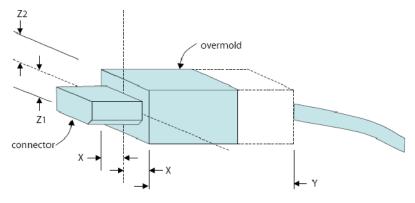

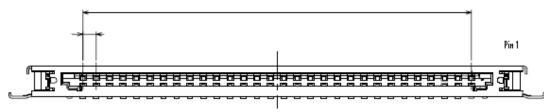

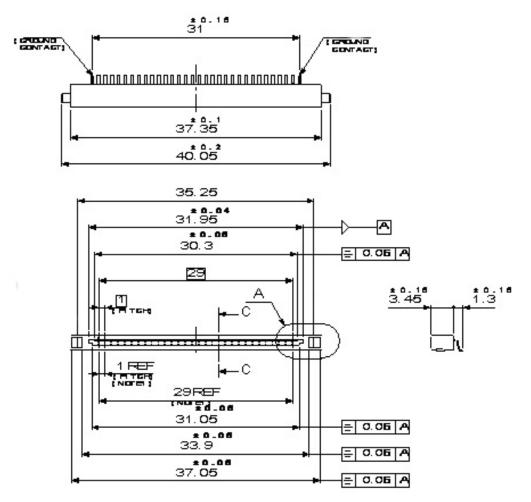

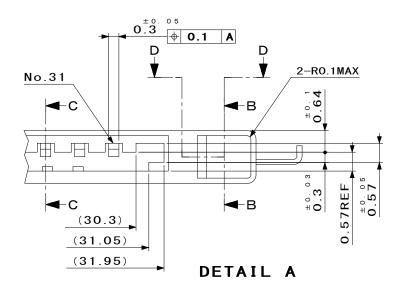

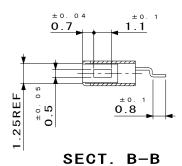

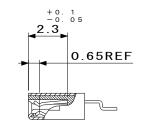

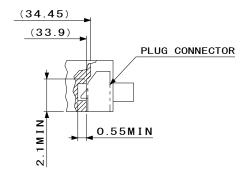

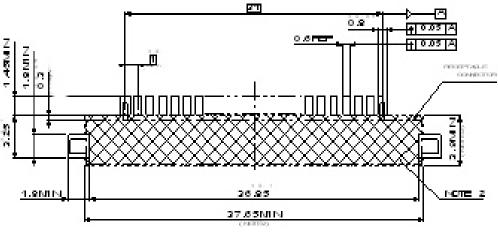

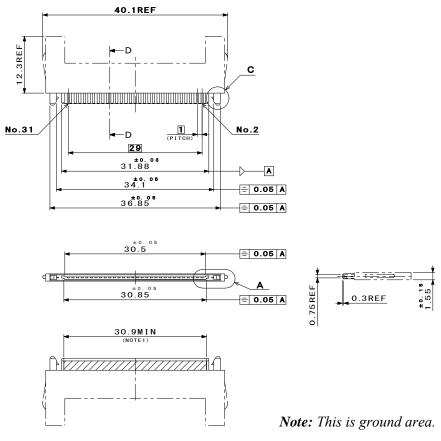

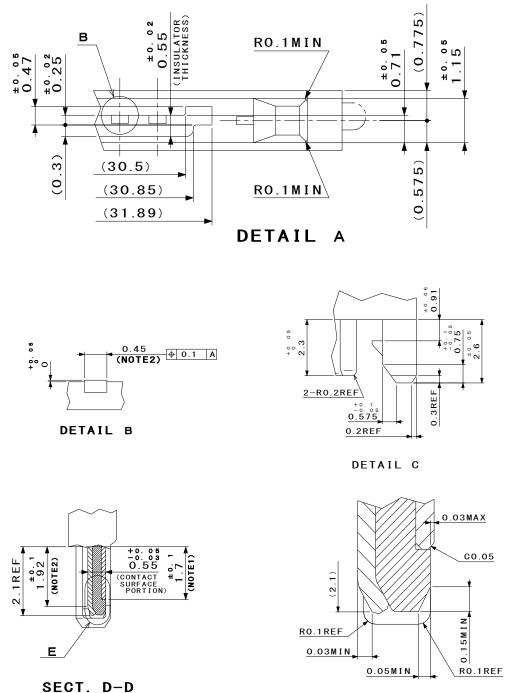

| 4.1  | Cable-0   | Connector Assembly Specifications (for Box-to-box)                | 911  |

|      | 4.1.1     | Cable-Connector Assembly Definition                               | 912  |

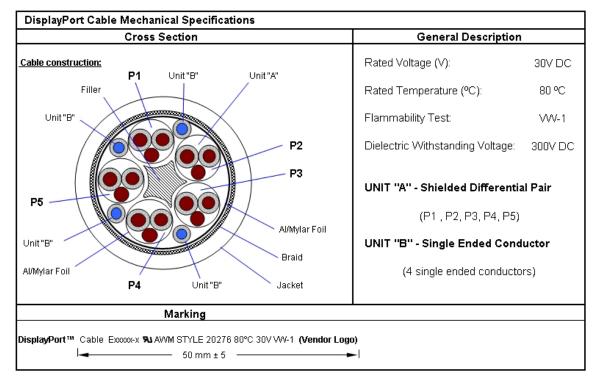

|      | 4.1.2     | Bulk Cable Type                                                   | 916  |

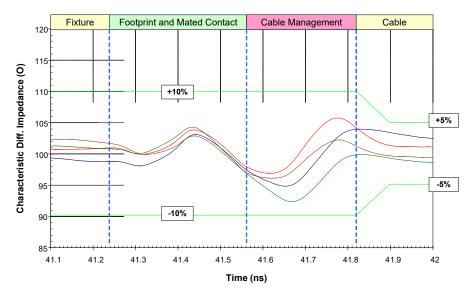

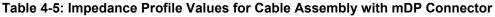

|      | 4.1.3     | Impedance Profile                                                 | 917  |

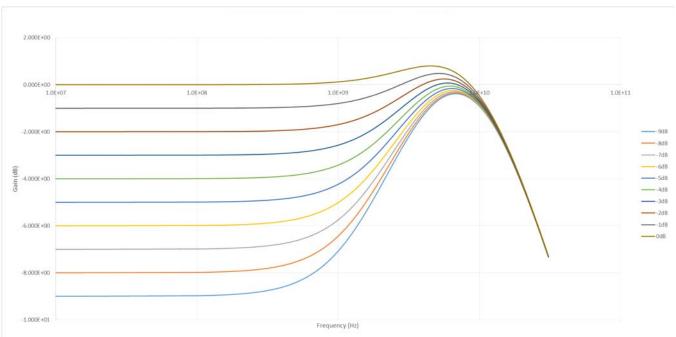

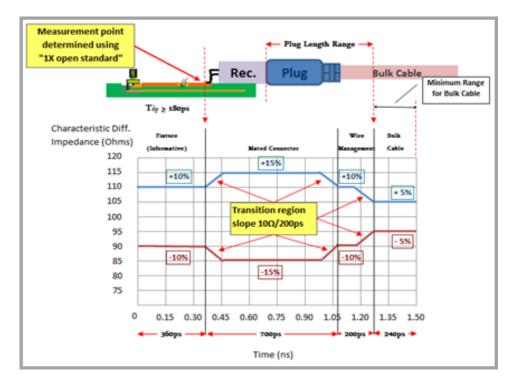

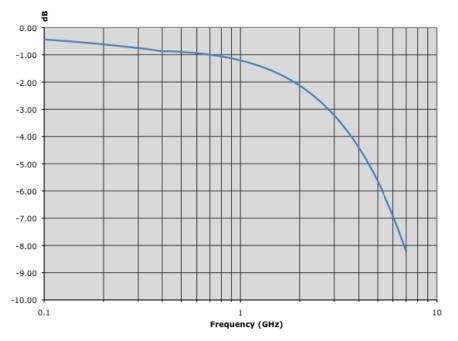

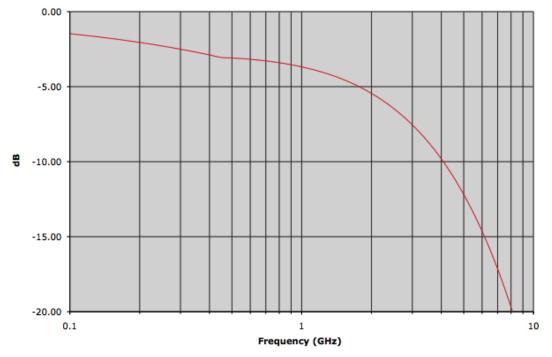

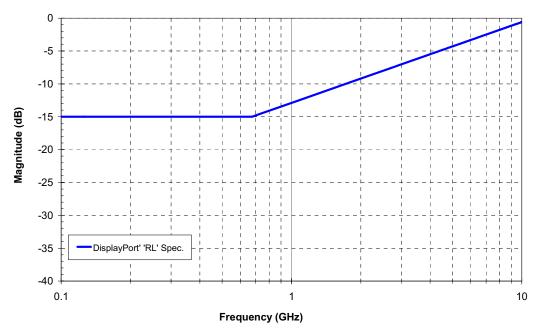

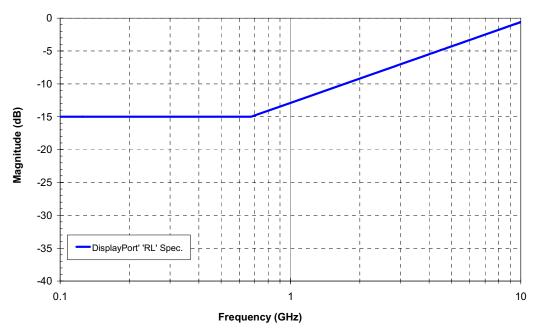

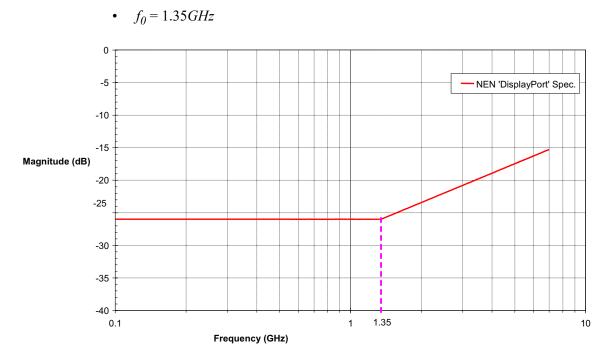

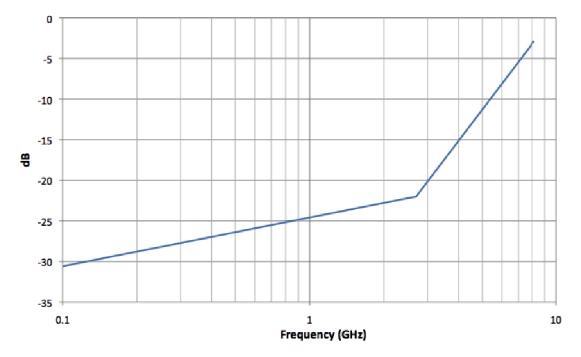

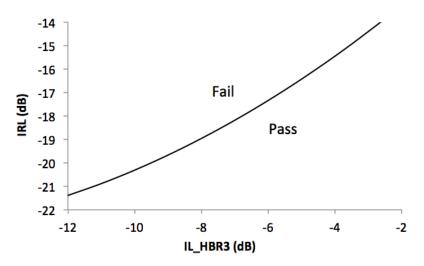

|      | 4.1.4     | Insertion Loss and Return Loss                                    |      |

|      | 4.1.5     | High Bit Rate Cable-Connector Assembly Specification              |      |

|      | 4.1.6     | Reduced Bit Rate Cable-Connector Assembly Specification           | 931  |

|      | 4.1.7     | DP8K Cable Specification                                          | 935  |

|      | 4.1.8     | Bulk Cable and Connector Impedance (Normative)                    | 939  |

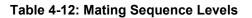

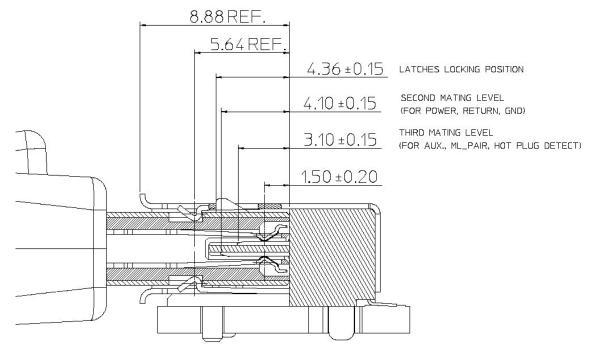

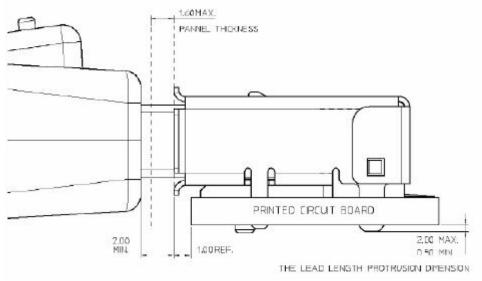

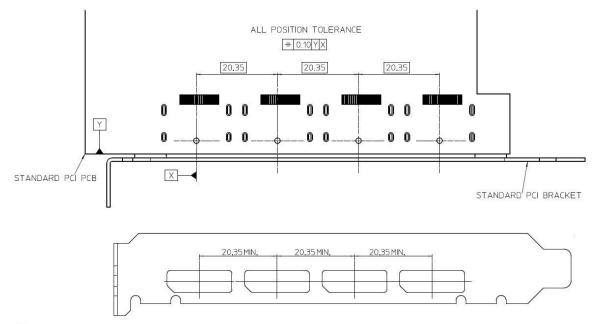

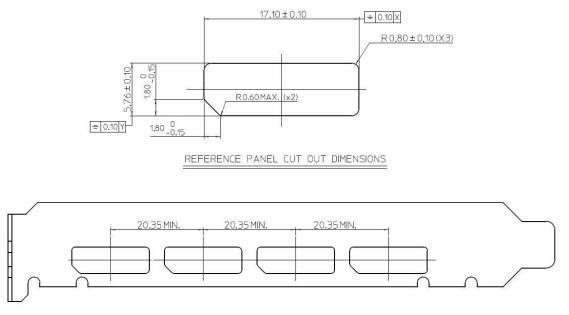

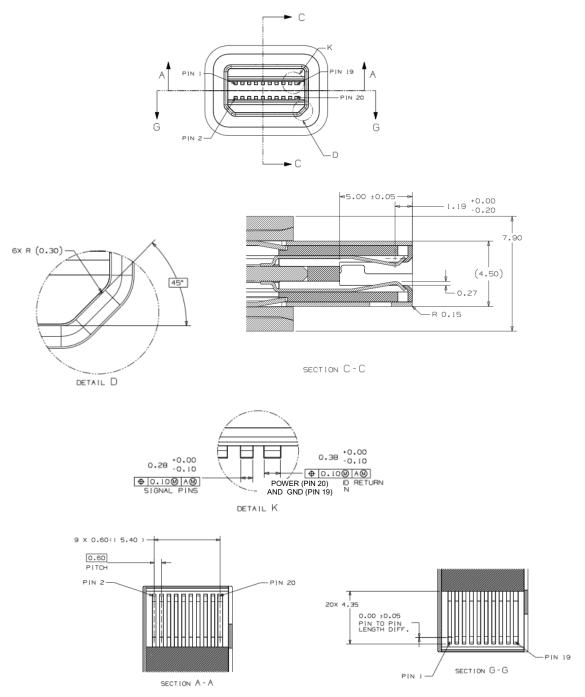

| 4.2  | Connec    | ctor Specification                                                | 940  |

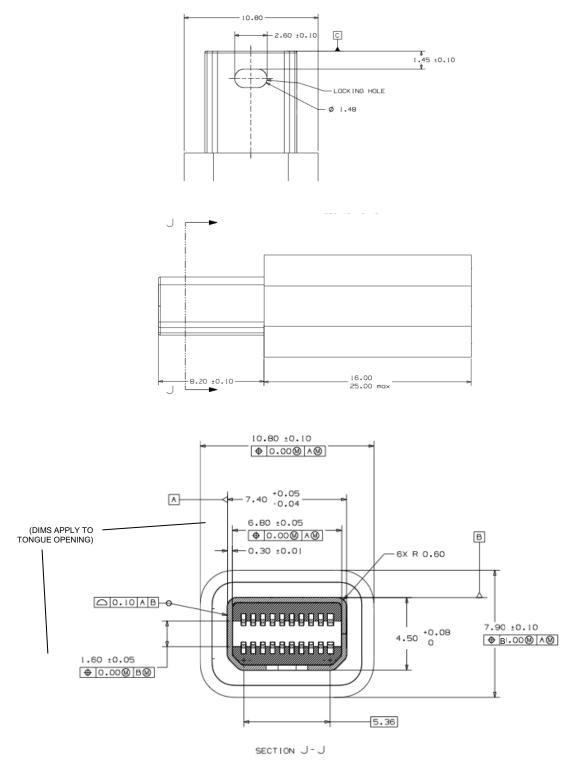

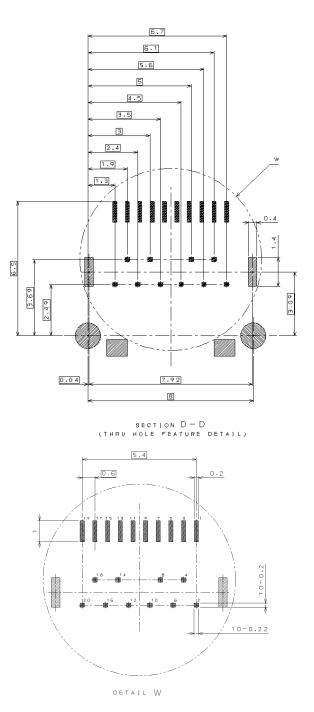

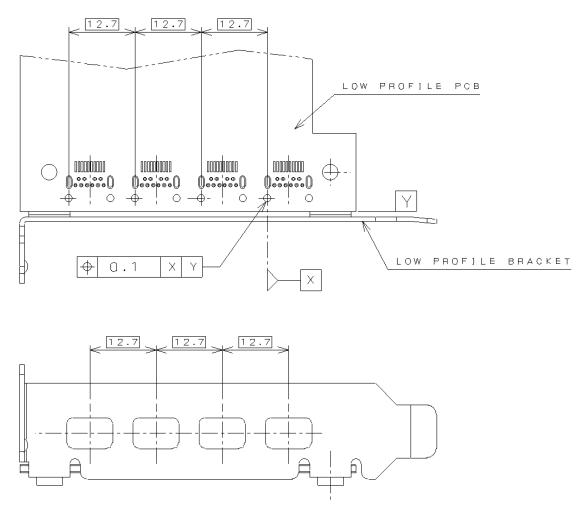

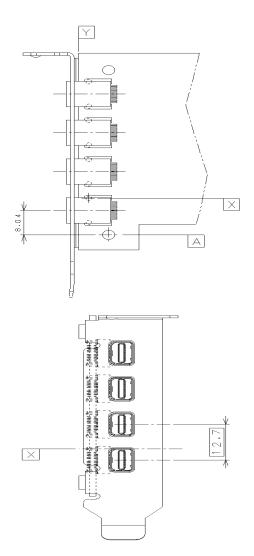

|      | 4.2.1     | External Full-size Connector.                                     | 940  |

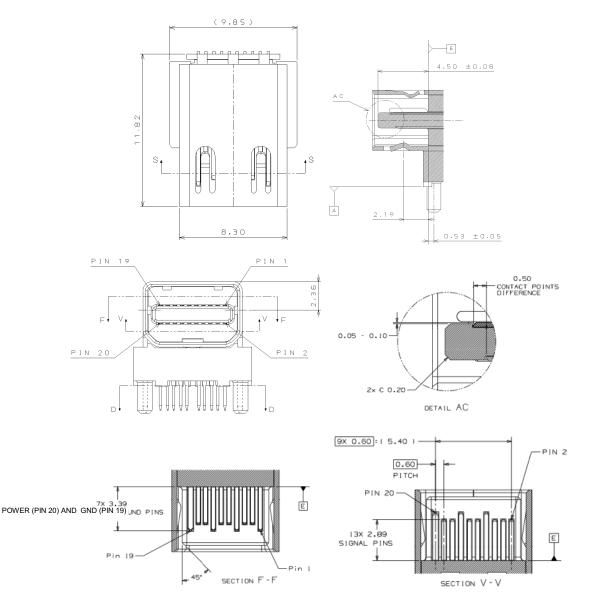

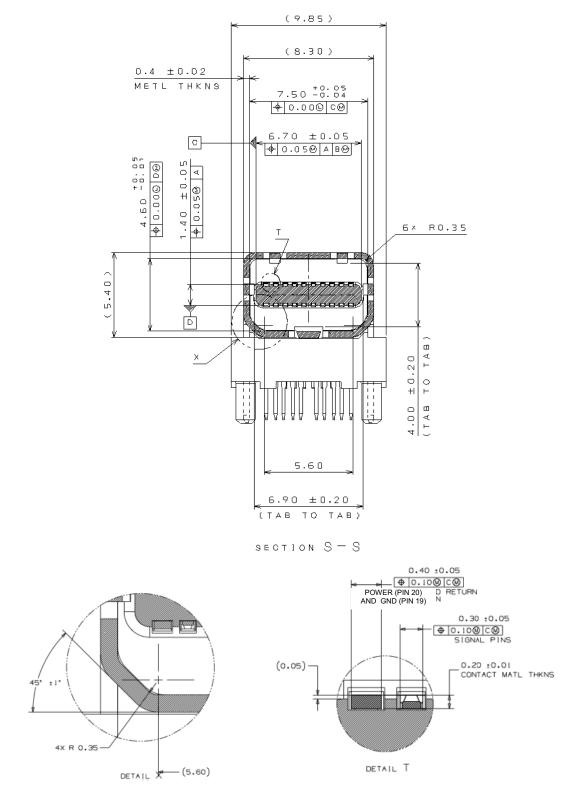

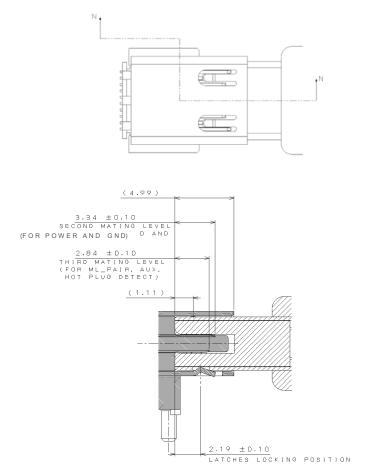

|      | 4.2.2     | mDP External Connector                                            | 953  |

|      | 4.2.3     | Panel-side Internal Connector (Informative)                       | 974  |

|      |           |                                                                   |      |

Section 4

| Section 5 | Sour | ce/Sink | /Branch Device Policy Requirements for Interoperability          | 983  |

|-----------|------|---------|------------------------------------------------------------------|------|

|           | 5.1  | DP SS   | ST Source Device with 8b/10b Channel Coding                      | 983  |

|           |      | 5.1.1   | Stream Source Requirement                                        | 983  |

|           |      | 5.1.2   | Source Device Link Configuration Requirement                     | 988  |

|           |      | 5.1.3   | Source Device Behavior on Stream Timing Change                   | 990  |

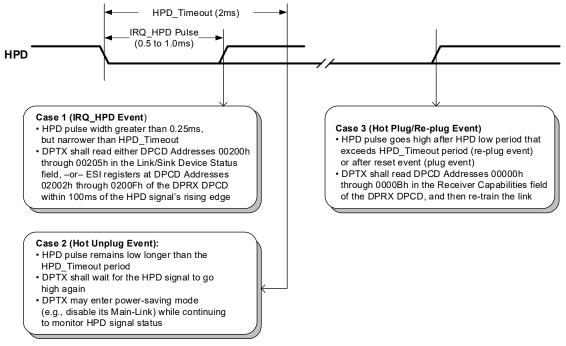

|           |      | 5.1.4   | Source Device Behavior upon HPD Pulse Detection                  | 991  |

|           |      | 5.1.5   | Downstream Device DPRX Power Management by a Source Device       | 992  |

|           |      | 5.1.6   | Source Device Connected to a Branch Device                       | 993  |

|           |      | 5.1.7   | Source Device DSC Bitstream Transport and FEC Policy             | 995  |

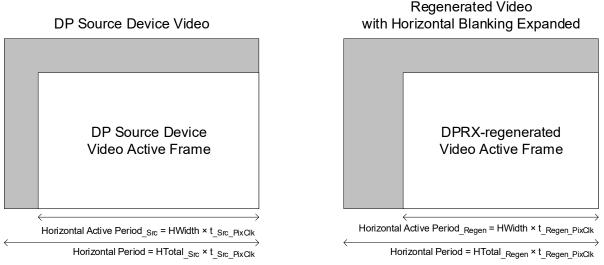

|           |      | 5.1.8   | Horizontal Blanking Expansion Support                            | 995  |

|           | 5.2  | DP SS   | ST Sink Device with 8b/10b Channel Coding                        | 996  |

|           |      | 5.2.1   | Stream Sink Requirement                                          | 996  |

|           |      | 5.2.2   | Sink Device Link Configuration Requirement                       |      |

|           |      | 5.2.3   | Sink Device Behavior on Stream Timing Change                     | 999  |

|           |      | 5.2.4   | Toggling of HPD Signal for Status Change Notification            |      |

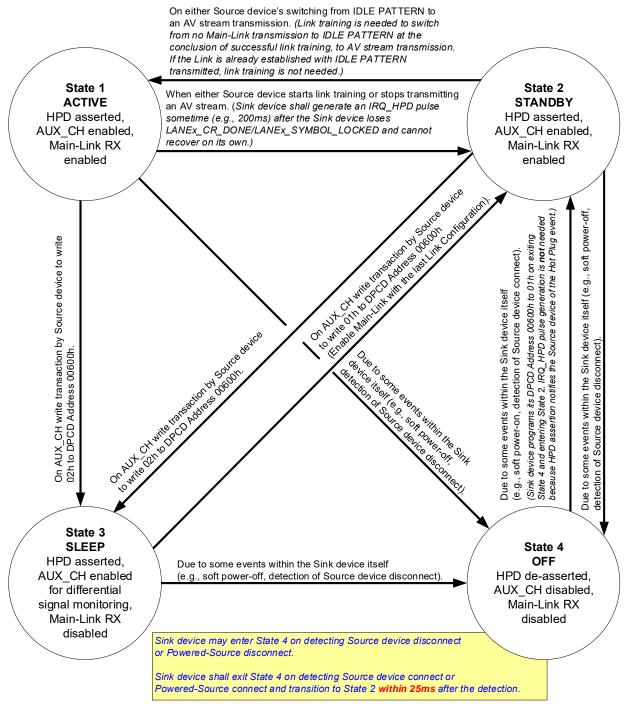

|           |      | 5.2.5   | Sink Device DPRX Power State                                     |      |

|           |      | 5.2.6   | Sink Device DSC Bitstream Handling and FEC Policy                | 1005 |

|           | 5.3  | DP SS   | T-only Branch Device with 8b/10b Channel Coding                  |      |

|           |      | 5.3.1   | DisplayID or Legacy EDID Access Handling Requirement.            | 1006 |

|           |      | 5.3.2   | Branch Device Link Configuration Requirements                    |      |

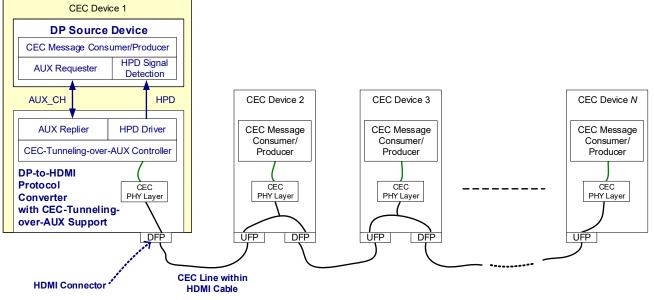

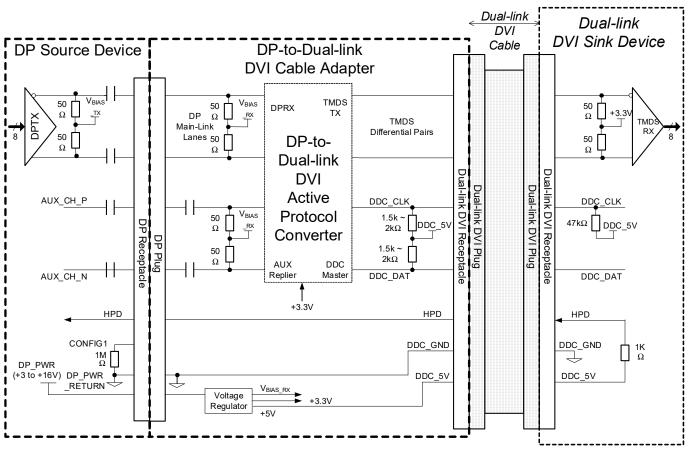

|           |      | 5.3.3   | Active Protocol Converter Adapters                               |      |

|           |      | 5.3.4   | Link Rate and Lane Count                                         | 1018 |

|           |      | 5.3.5   | Forward Error Correction                                         | 1018 |

|           | 5.4  | DP M    | ST Source Device with 8b/10b Channel Coding                      | 1019 |

|           |      | 5.4.1   | Prompting the Downstream Device MST/SST Capabilities Transition. |      |

|           |      | 5.4.2   | Atomic Message Transaction Generation                            | 1019 |

|           |      | 5.4.3   | Connection Status Notify Message Transaction Handling            | 1019 |

|           |      | 5.4.4   | Power Management.                                                | 1019 |

|           |      | 5.4.5   | DSC Bitstream Transport and FEC Policy                           | 1020 |

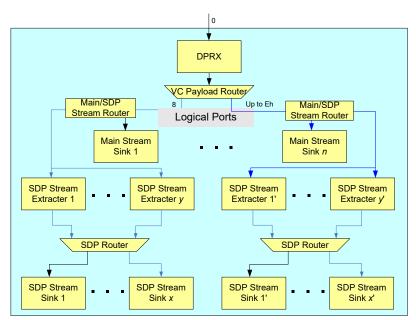

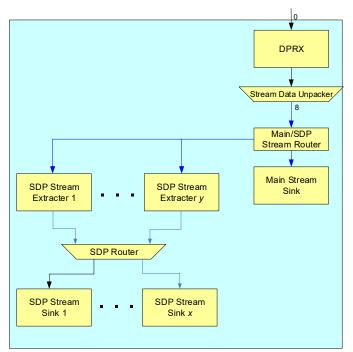

|           | 5.5  | DP M    | ST Sink Device with 8b/10b Channel Coding                        |      |

|           |      | 5.5.1   | MST Sink Device with a DPRX in a Single UFP                      | 1021 |

|           |      | 5.5.2   | MST Sink Device with a DPRX in Multiple UFPs                     | 1023 |

|           | 5.6  | DP M    | ST Branch Device with 8b/10b Channel Coding                      | 1024 |

|           |      | 5.6.1   | MST Branch Device with a DPRX in a Single UFP                    | 1024 |

|           |      | 5.6.2   | MST Branch Device with a DPRX in Multiple UFPs                   | 1028 |

|           | 5.7  | DP So   | burce Device with 128b/132b Channel Coding Enabled               |      |

|           |      | 5.7.1   | Video Fallback Mode                                              |      |

|           |      | 5.7.2   | Configuring LTTPR-capable PHY Repeaters                          | 1029 |

|           |      | 5.7.3   | DSC Support                                                      |      |

|           |      | 5.7.4   | HDCP Encryption Status Change                                    |      |

|           |      | 5.7.5   | Allocation Change Trigger                                        |      |

|           |      | 5.7.6   | AUX Message Transaction Support                                  |      |

|           |      | 5.7.7   | Panel Replay Optimization for DP Tunneling                       |      |

|           |      |         | · - · · ·                                                        |      |

|            | 5.8      | DP Sink Device with 128b/132b Channel Coding Enabled.               | 1030  |

|------------|----------|---------------------------------------------------------------------|-------|

|            |          | 5.8.1 Video Fallback Mode                                           | 1030  |

|            |          | 5.8.2 DSC Support                                                   | 1030  |

|            |          | 5.8.3 HDCP Encryption Status Change                                 | 1030  |

|            |          | 5.8.4 Allocation Change Trigger                                     | 1030  |

|            | 5.9      | DP Branch Device with 128b/132b Channel Coding Enabled              | 1031  |

|            |          | 5.9.1 DFP Configurations                                            | 1031  |

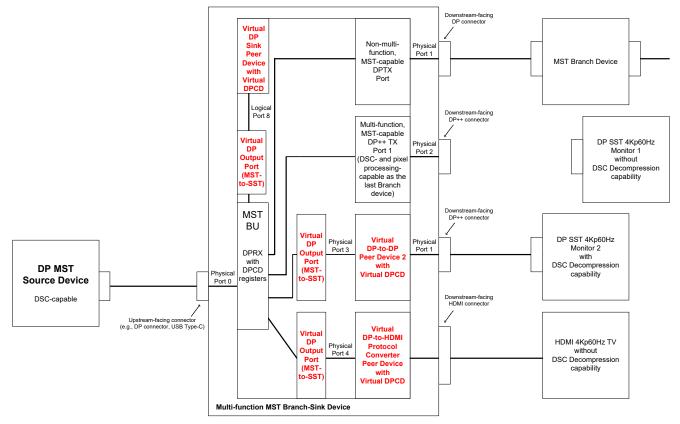

|            |          | 5.9.2 Virtual DP Peer Device                                        | 1031  |

|            |          | 5.9.3 DSC Support                                                   | 1031  |

|            |          | 5.9.4 Encryption Status Change                                      | 1031  |

|            |          | 5.9.5 Allocation Change Trigger                                     | 1031  |

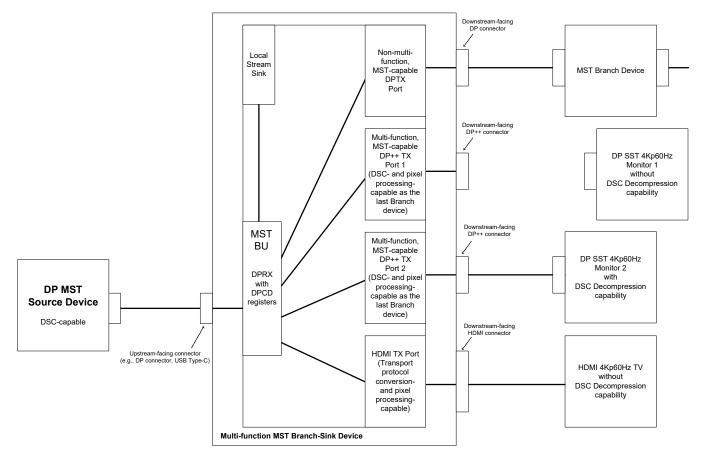

|            | 5.10     | Branch-Sink Device in 8b/10b MST Mode                               | 1032  |

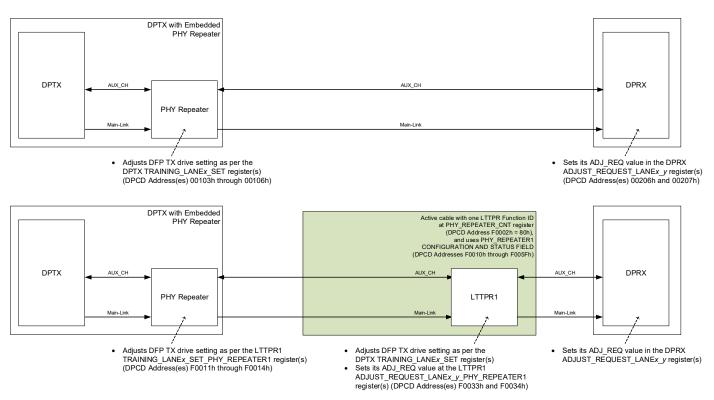

|            | 5.11     | DP Source or Branch Device with an Embedded PHY Repeater on the DFP | 1032  |

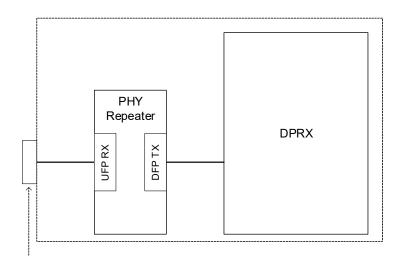

|            | 5.12     | DP Sink or Branch Device with an Embedded PHY Repeater on the UFP   | 1033  |

|            | 5.13     | Cable-Connector Assembly                                            | 1034  |

|            |          | 5.13.1 Box-to-Box, User-Detachable Cable Assembly                   | 1034  |

|            |          | 5.13.2 Embedded and Captive Cable Assembly                          | 1034  |

|            |          | 5.13.3 Active Cable Assembly                                        | 1034  |

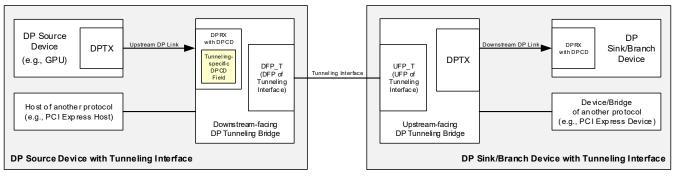

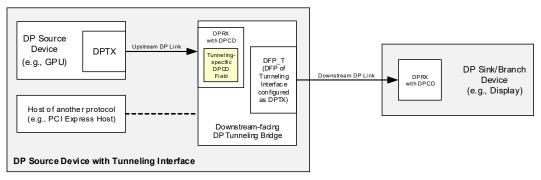

|            | 5.14     | DP Tunneling                                                        | 1045  |

|            |          | 5.14.1 Panel Replay Optimization with DP Tunneling                  | 1046  |

|            | <b>.</b> | -                                                                   | 40.40 |

| Appendix A |          | o Transport (Informative)                                           |       |

|            | A.1      | Audio Stream Components                                             |       |

|            | A.2      | Association of Three SDP Types by way of Packet ID                  |       |

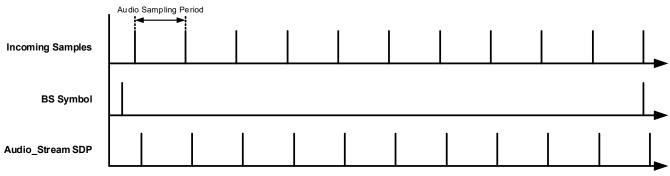

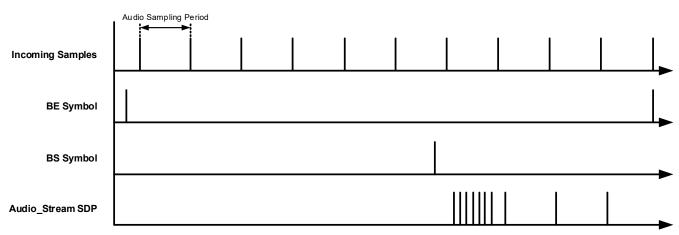

|            | A.3      | Scheduling of Audio_Stream SDP Transmission                         |       |

|            |          | A.3.1 Audio Format Change Handling                                  |       |

|            | A.4      | Audio_Stream SDP Structure.                                         |       |

|            |          | A.4.1 1- or 2-channel L-PCM Audio                                   |       |

|            |          | A.4.2 3- to 8-channel Audio                                         |       |

|            |          | A.4.3 1- to 2-channel One Bit Audio                                 |       |

|            |          | A.4.4 3- to 8-channel One Bit Audio                                 |       |

|            |          | A.4.5 1- to 16-Channel L-PCM 3D Audio                               |       |

|            |          | A.4.6 17- to 32-Channel L-PCM 3D Audio                              |       |

|            |          | A.4.7 DST Audio                                                     |       |

|            | A.5      | Channel-to-Speaker Mapping                                          |       |

|            | A.6      | Transfer of Sample Frequency Information                            | 1058  |

| Appendix B | Sink     | Event Notification Example (Informative)                            | 1059  |

|            | B.1      | Mutual Identification by Source and Sink Devices                    |       |

|            | B.2      | IRQ HPD Pulse and Sink Device-specific IRQ                          |       |

|            |          |                                                                     |       |

| Appendix C |          | Quality Management (Informative)                                    |       |

|            | C.1      | Marginal Link Quality                                               |       |

|            | C.2      | Analysis                                                            |       |

|            | C.3      | Tolerance to Bit Errors.                                            |       |

|            | C.4      | Link Retraining                                                     |       |

|            | C.5      | Long-term Link Quality Monitoring (Guidelines)                      | 1062  |

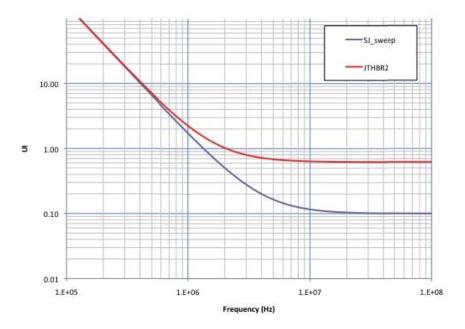

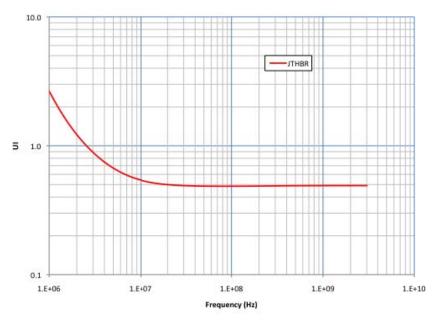

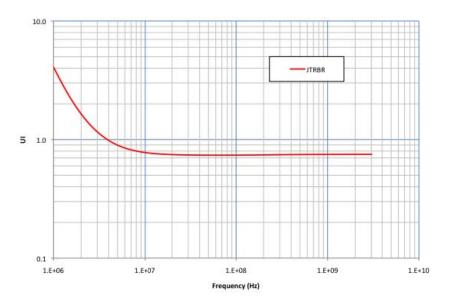

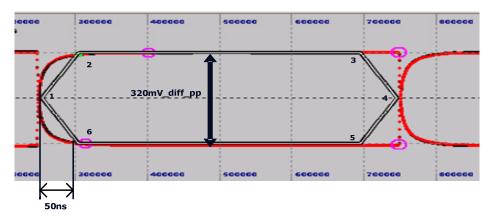

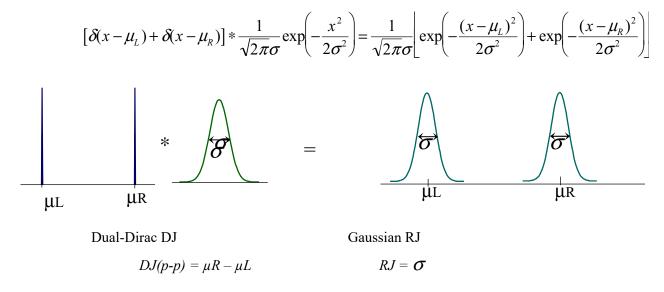

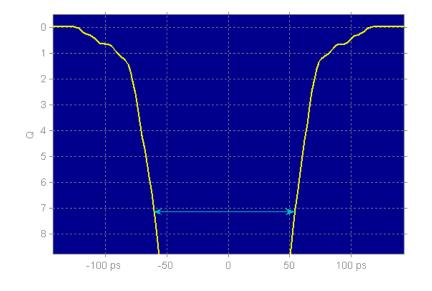

| Appendix D | HBR2 Electrical Specifications (Informative).1063D.1AUX Parameters.1063D.2Main-Link Parameters.1064D.3Dual-Dirac Jitter Model.1069                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

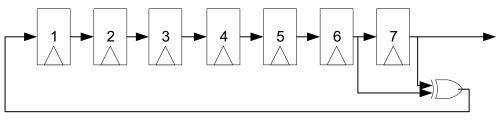

| Appendix E | HBRx/RBR Scrambler C Code Reference (Informative)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Appendix F | Topology Management/Payload Bandwidth Management Usage<br>Examples (Informative)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

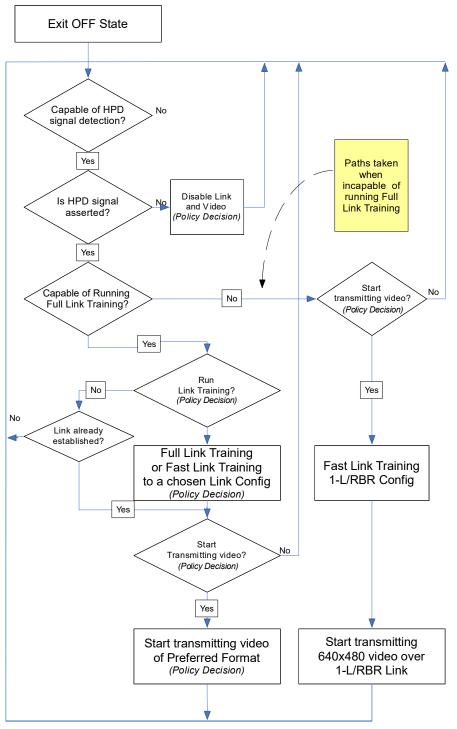

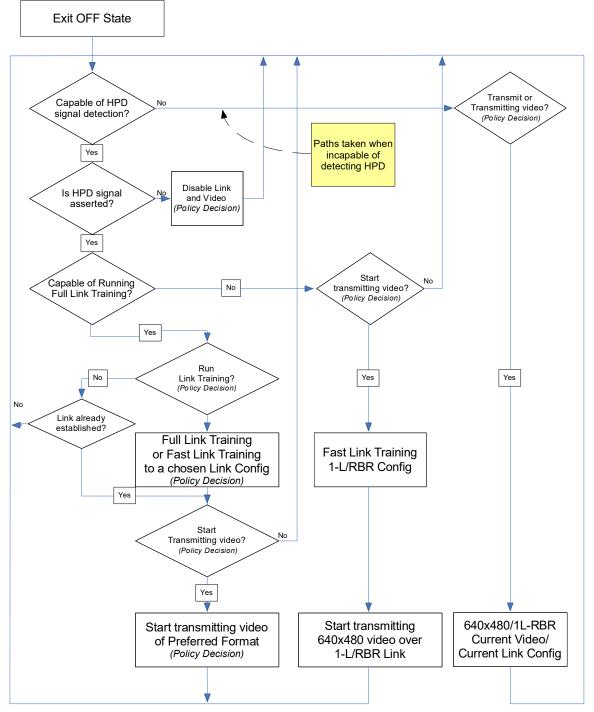

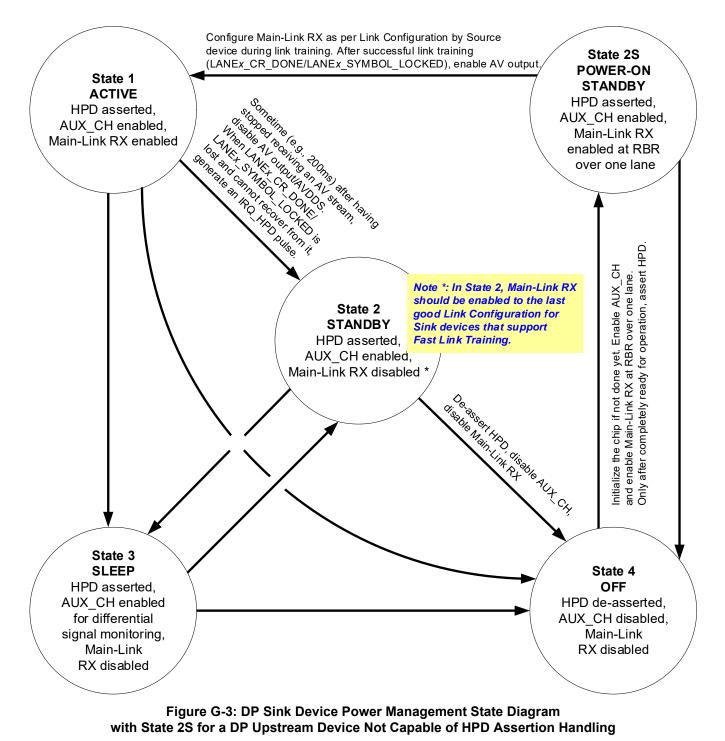

| Appendix G | Link Management during System Initialization (Informative)1079G.1Background                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

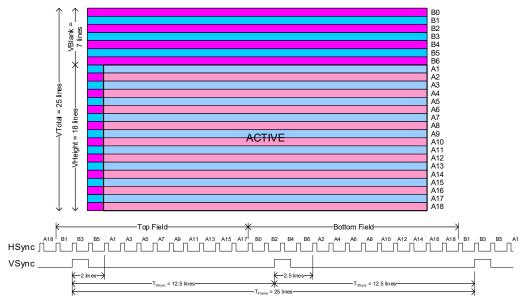

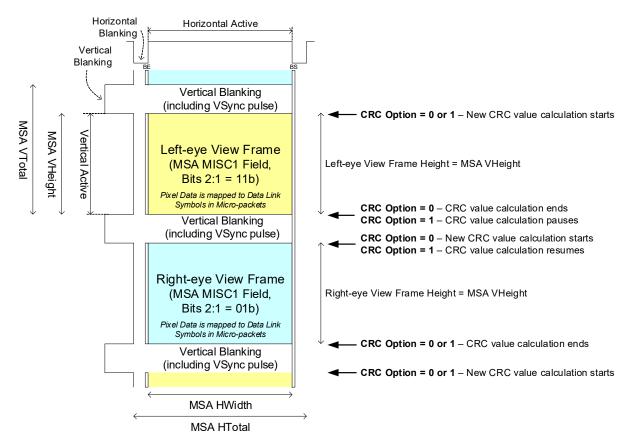

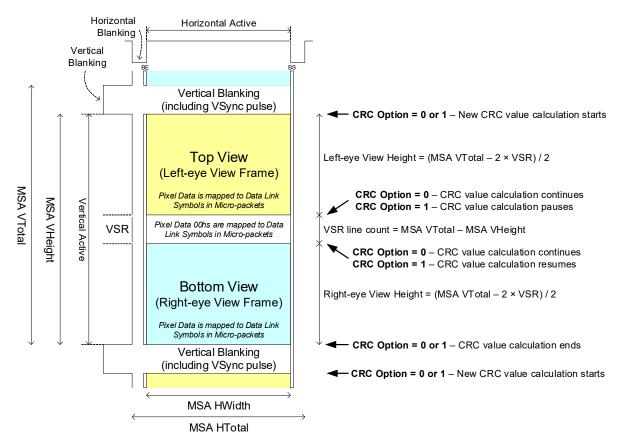

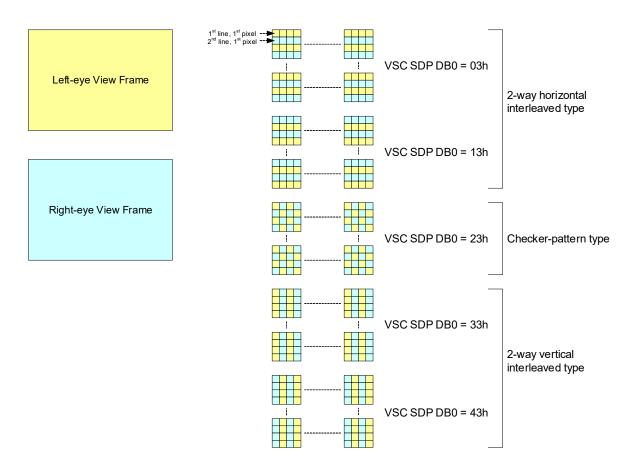

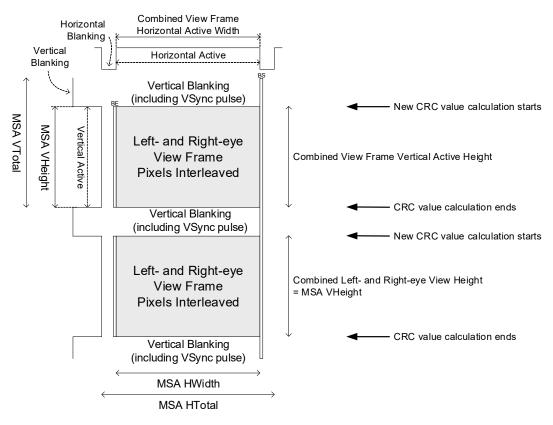

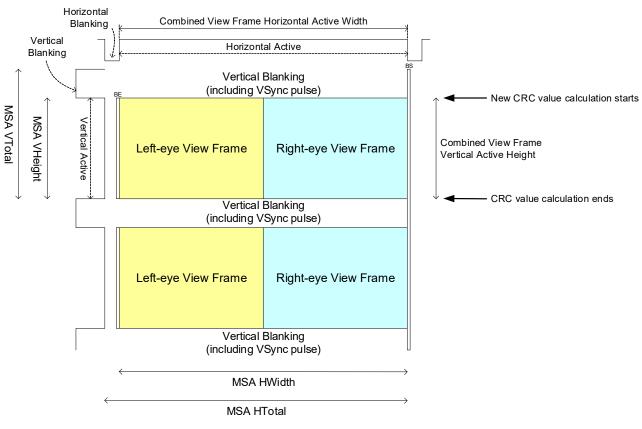

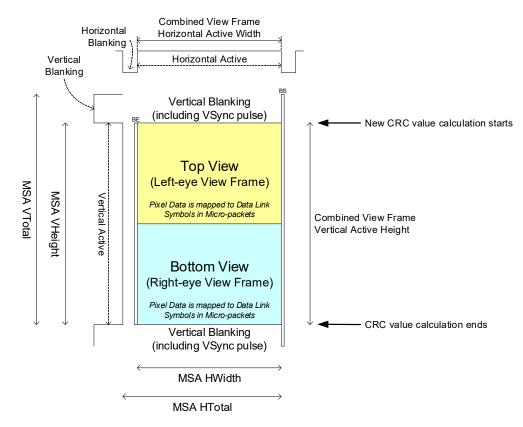

| Appendix H | <b>3D Stereo Display Protocol Support.</b> 1085H.1In-band 3D Stereo Signaling Methods.1085H.1.1MSA MISC1 Method1085H.1.2VSC SDP Method.1086                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|            | <ul> <li>H.2 3D Stereo Display Capability Declaration</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

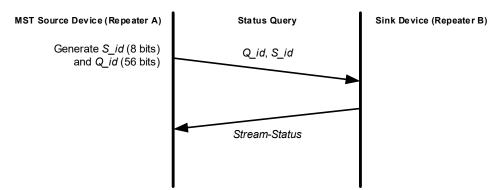

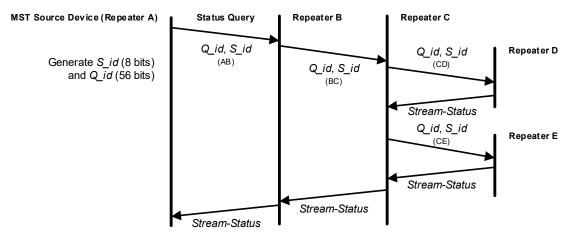

| Appendix I | H.3.2       DP 3D Stereo Video Source Device Support       .1104         QUERY_STREAM_ENCRYPTION_STATUS Message Transaction       1105         I.1       Self-checking by MST Branch Devices       .1105         I.2       Merit of QUERY_STREAM_ENCRYPTION_STATUS Message Transaction       .1105         I.3       QUERY_STREAM_ENCRYPTION_STATUS Message       .1105         I.3       QUERY_STREAM_ENCRYPTION_STATUS Message       .1106         I.3.1       IDs Provided by MST Source Device for       .1106         I.3.2       Stream Status in QUERY_STREAM_ENCRYPTION_STATUS Request       .1106         I.3.2       Stream Status in QUERY_STREAM_ENCRYPTION_STATUS       .1108         I.3.3       Stream Status Signature in       .1108         I.3.3       Stream Status Signature in       .1100         I.3.4       Usage of Sink Type in Stream Status by an MST Source Device       .1110 |

|            | I.3.5 Status Query                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Appendix L       Information and Examples for DSC Slice/Display Line         Calculations (Informative)       11         L.1       Derivation of Slice Count Requirements       11         L.2       Usage Example.       11         Appendix M       128b/132b Channel Coding without Using Place Holders       11         M.1       Stream Data-to-Link Symbol Mapping with<br>128b/132b Link Layer without Place Holders       11         M.2       Main-Link 128b/132b PHY Logical Sub-layer without Place Holders       11 | ppendix J | 16-Bit Frame CRC Example (Informative)                                                                                                                         |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

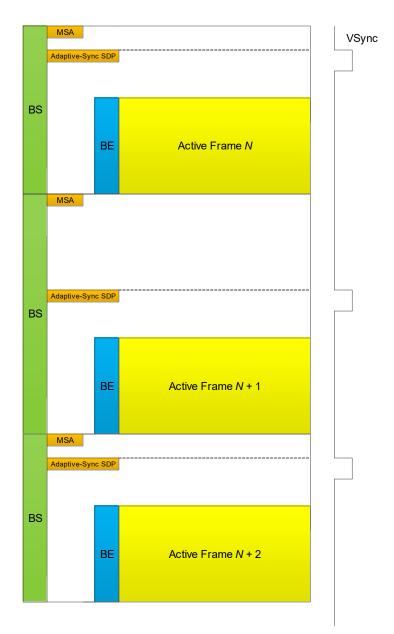

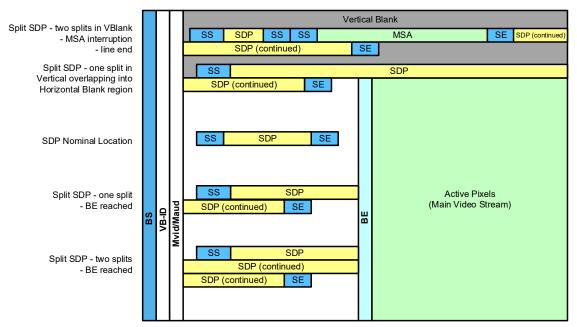

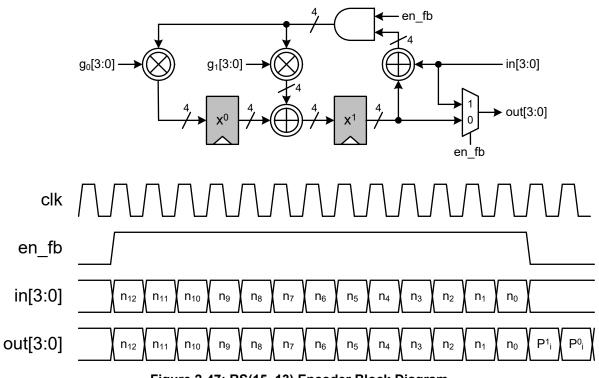

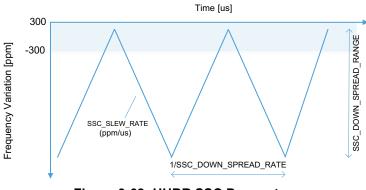

| Calculations (Informative)       11         L.1       Derivation of Slice Count Requirements       11         L.2       Usage Example       11         Appendix M       128b/132b Channel Coding without Using Place Holders       11         M.1       Stream Data-to-Link Symbol Mapping with<br>128b/132b Link Layer without Place Holders       11         M.2       Main-Link 128b/132b PHY Logical Sub-layer without Place Holders       11                                                                               | ppendix K | Adaptive-Sync 1115                                                                                                                                             |

| <ul> <li>M.1 Stream Data-to-Link Symbol Mapping with<br/>128b/132b Link Layer without Place Holders</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                   |           | Calculations (Informative)       1117         L.1       Derivation of Slice Count Requirements       .1117                                                     |

| <ul> <li>M.2.2 128b/132b PHY Logical Sub-layer Operating Sequence<br/>without Place Holders (Alternative to Section 3.5.2.2)</li></ul>                                                                                                                                                                                                                                                                                                                                                                                          |           | <ul> <li>128b/132b Link Layer without Place Holders</li></ul>                                                                                                  |

| N.1       UHBRx PRBS7       11         N.2       UHBRx PRBS9       11         N.3       UHBRx PRBS11       11         N.4       UHBRx PRBS15       11         N.5       UHBRx PRBS23       11         N.6       UHBRx PRBS31       11                                                                                                                                                                                                                                                                                           |           | N.2       UHBRx PRBS9       1132         N.3       UHBRx PRBS11       1132         N.4       UHBRx PRBS15       1133         N.5       UHBRx PRBS23       1133 |

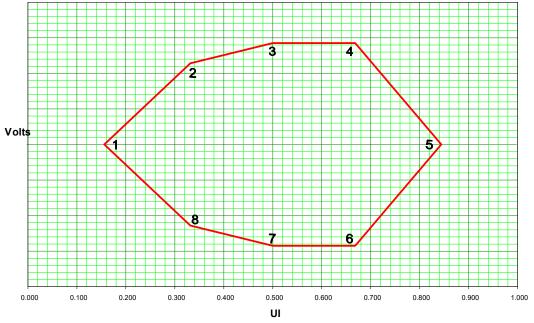

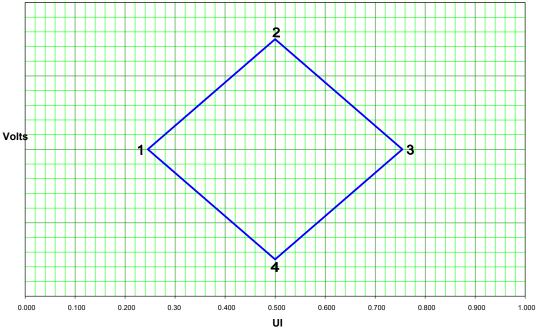

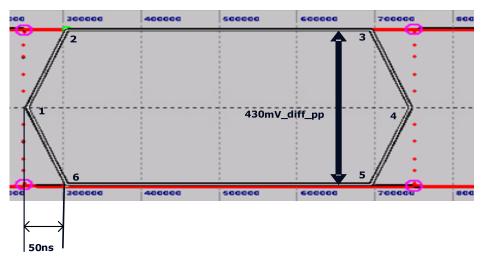

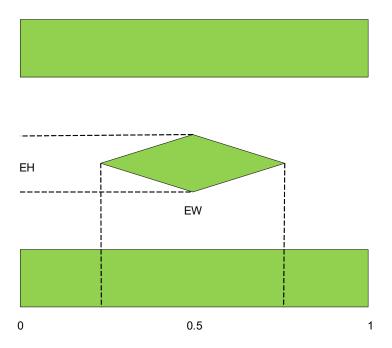

| O.2 UHBR <i>x</i> EYE Mask                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |           |                                                                                                                                                                |

## Tables

| Table 1:    | Patents                                                     |

|-------------|-------------------------------------------------------------|

| Table 2:    | Main Contributors to <i>DP v2.0</i>                         |

| Table 3:    | Revision History                                            |

|             |                                                             |

| Table 1-1:  | Acronyms and Abbreviations                                  |

| Table 1-2:  | Glossary of Terms                                           |

| Table 1-3:  | Keywords                                                    |

| Table 1-4:  | Numbering                                                   |

| Table 1-5:  | Reference Documents                                         |

| Table 1-6:  | DP Main-Link Application Bandwidth                          |

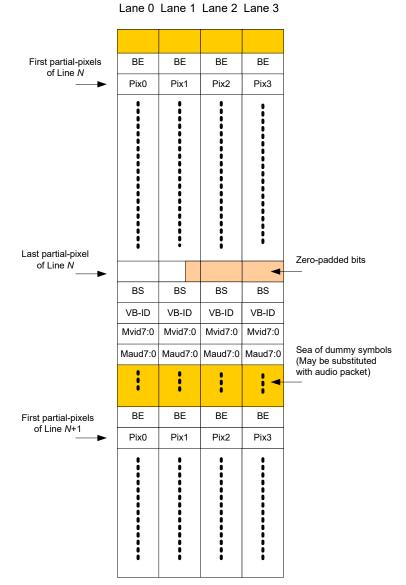

| Table 1-7:  | Pixel Data Mapping over 4-lane Main-Link                    |

| Table 2-1:  | Device Types Covered by this Standard                       |

| Table 2-2:  | Topological Device Categories                               |

| Table 2-3:  | Default Framing Mode Control Link Symbols                   |

| Table 2-4:  | Default Framing Mode (Deprecated) to                        |

|             | Enhanced Framing Mode Control Link Symbol Mapping           |

| Table 2-5:  | Pixel Steering into Main-Link Lanes                         |

| Table 2-6:  | VB-ID Bit Definition                                        |

| Table 2-7:  | 10bpc RGB (30bpp) 1366x768 Packing to a 4-Lane Main-Link104 |

| Table 2-8:  | 6bpc RGB Mapping to a 4-Lane Main-Link                      |

| Table 2-9:  | 6bpc RGB Mapping to a 2-Lane Main-Link106                   |

| Table 2-10: | 6bpc RGB Mapping to a 1-Lane Main-Link106                   |

| Table 2-11: | 8bpc RGB to a 4-Lane Main-Link Mapping107                   |

| Table 2-12: | 8bpc RGB Mapping to a 2-Lane Main-Link                      |

| Table 2-13: | 8bpc RGB Mapping to a 1-Lane Main-Link                      |

| Table 2-14: | 10bpc RGB Mapping to a 4-Lane Main-Link                     |

| Table 2-15: | 10bpc RGB Mapping to a 2-Lane Main-Link                     |

| Table 2-16: | 10bpc RGB Mapping to a 1-Lane Main-Link                     |

| Table 2-17: | 12bpc RGB Mapping to a 4-Lane Main-Link                     |

| Table 2-18: | 12bpc RGB Mapping to a 2-Lane Main-Link                     |

| Table 2-19: | 12bpc RGB Mapping to a 1-Lane Main-Link                     |

| Table 2-20: | 16bpc RGB Mapping to a 4-Lane Main-Link                     |

| Table 2-21: | 16bpc RGB Mapping to a 2-Lane Main-Link                     |

| Table 2-22: | 16bpc RGB Mapping to a 1-Lane Main-Link                     |

| Table 2-23: | 8bpc YCbCr 4:2:2 Mapping to a 4-Lane Main-Link              |

| Table 2-24: | 8bpc YCbCr 4:2:2 Mapping to a 2-Lane Main-Link              |

| Table 2-25: | 8bpc YCbCr 4:2:2 Mapping to a 1-Lane Main-Link              |

| Table 2-26: | 10bpc YCbCr 4:2:2 Mapping to a 4-Lane Main-Link             |

| Table 2-27: | 10bpc YCbCr 4:2:2 Mapping to a 2-Lane Main-Link             |

| Table 2-28: | 10bpc YCbCr 4:2:2 Mapping to a 1-Lane Main-Link             |

| Table 2-29: | 12bpc YCbCr 4:2:2 Mapping to a 4-Lane Main-Link             |

|             |                                                             |

| Table 2-30:                | 12bpc YCbCr 4:2:2 Mapping to a 2-Lane Main-Link                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Table 2-31:                | 12bpc YCbCr 4:2:2 Mapping to a 1-Lane Main-Link.       115                       |

| Table 2-32:                | 16bpc YCbCr 4:2:2 Mapping to a 4-Lane Main-Link.       116                       |

| Table 2-33:                | 16bpc YCbCr 4:2:2 Mapping to a 2-Lane Main-Link.       116                       |

| Table 2-34:                | 16bpc YCbCr 4:2:2 Mapping to a 1-Lane Main-Link.       116                       |

| Table 2-34:                | 8bpc YCbCr 4:2:0 Even Lines (Starting with Line 0) over Four Main-Link Lanes 117 |

| Table 2-35:                | 8bpc YCbCr 4:2:0 Odd Lines (Starting with Line 0) over Four Main-Link Lanes117   |

| Table 2-30.<br>Table 2-37: | 8bpc YCbCr 4:2:0 Even Lines (Starting with Line 0) over Two Main-Link Lanes118   |

| Table 2-37.<br>Table 2-38: | 8bpc YCbCr 4:2:0 Odd Lines (Starting with Line 0) over Two Main-Link Lanes118    |

|                            |                                                                                  |

| Table 2-39:                | 8bpc YCbCr 4:2:0 Even Lines (Starting with Line 0) over One Main-Link Lane       |

| Table 2-40:                | 8bpc YCbCr 4:2:0 Odd Lines (Starting with Line 0) over One Main-Link Lane118     |

| Table 2-41:                | 10bpc YCbCr 4:2:0 Even Lines (Starting with Line 0) over Four Main-Link Lanes119 |

| Table 2-42:                | 10bpc YCbCr 4:2:0 Odd Lines (Starting with Line 0) over Four Main-Link Lanes119  |

| Table 2-43:                | 10bpc YCbCr 4:2:0 Even Lines (Starting with Line 0) over Two Main-Link Lanes 120 |

| Table 2-44:                | 10bpc YCbCr 4:2:0 Odd Lines (Starting with Line 0) over Two Main-Link Lanes 120  |

| Table 2-45:                | 10bpc YCbCr 4:2:0 Even Lines (Starting with Line 0) over One Main-Link Lane121   |

| Table 2-46:                | 10bpc YCbCr 4:2:0 Odd Lines (Starting with Line 0) over One Main-Link Lane121    |

| Table 2-47:                | 12bpc YCbCr 4:2:0 Even Lines (Starting with Line 0) over Four Main-Link Lanes122 |

| Table 2-48:                | 12bpc YCbCr 4:2:0 Odd Lines (Starting with Line 0) over Four Main-Link Lanes122  |

| Table 2-49:                | 12bpc YCbCr 4:2:0 Even Lines (Starting with Line 0) over Two Main-Link Lanes 123 |

| Table 2-50:                | 12bpc YCbCr 4:2:0 Odd Lines (Starting with Line 0) over Two Main-Link Lanes 123  |

| Table 2-51:                | 12bpc YCbCr 4:2:0 Even Lines (Starting with Line 0) over One Main-Link Lane124   |

| Table 2-52:                | 12bpc YCbCr 4:2:0 Odd Lines (Starting with Line 0) over One Main-Link Lane124    |

| Table 2-53:                | 16bpc YCbCr 4:2:0 Even Lines (Starting with Line 0) over Four Main-Link Lanes125 |

| Table 2-54:                | 16bpc YCbCr 4:2:0 Odd Lines (Starting with Line 0) over Four Main-Link Lanes125  |

| Table 2-55:                | 16bpc YCbCr 4:2:0 Even Lines (Starting with Line 0) over Two Main-Link Lanes 126 |

| Table 2-56:                | 16bpc YCbCr 4:2:0 Odd Lines (Starting with Line 0) over Two Main-Link Lanes 126  |

| Table 2-57:                | 16bpc YCbCr 4:2:0 Even Lines (Starting with Line 0) over One Main-Link Lane127   |

| Table 2-58:                | 16bpc YCbCr 4:2:0 Odd Lines (Starting with Line 0) over One Main-Link Lane127    |

| Table 2-59:                | 8bpp Y-only to a 4-Lane Main-Link Mapping128                                     |

| Table 2-60:                | 8bpp Y-only Mapping to a 2-Lane Main-Link    128                                 |

| Table 2-61:                | 8bpp Y-only Mapping to a 1-Lane Main-Link    128                                 |

| Table 2-62:                | 10bpp Y-only Mapping to a 4-Lane Main-Link                                       |

| Table 2-63:                | 10bpp Y-only Mapping to a 2-Lane Main-Link                                       |

| Table 2-64:                | 10bpp Y-only Mapping to a 1-Lane Main-Link                                       |

| Table 2-65:                | 12bpp Y-only Mapping to a 4-Lane Main-Link                                       |

| Table 2-66:                | 12bpp Y-only Mapping to a 2-Lane Main-Link                                       |

| Table 2-67:                | 12bpp Y-only Mapping to a 1-Lane Main-Link                                       |

| Table 2-68:                | 16bpp Y-only Mapping to a 4-Lane Main-Link                                       |

| Table 2-69:                | 16bpp Y-only Mapping to a 2-Lane Main-Link                                       |

| Table 2-70:                | 16bpp Y-only Mapping to a 1-Lane Main-Link                                       |

| Table 2-71:                | 6bpp RAW Mapping to a 4-Lane Main-Link                                           |

| Table 2-72:                | 6bpp RAW Mapping to a 2-Lane Main-Link                                           |

| Table 2-73:                | 6bpp RAW Mapping to a 1-Lane Main-Link                                           |

|                            |                                                                                  |

| Table 2-74:  | 7bpp RAW Mapping to a 4-Lane Main-Link                                        | 133 |

|--------------|-------------------------------------------------------------------------------|-----|

| Table 2-75:  | 7bpp RAW Mapping to a 2-Lane Main-Link                                        | 133 |

| Table 2-76:  | 7bpp RAW Mapping to a 1-Lane Main-Link                                        | 133 |

| Table 2-77:  | 8bpp RAW Mapping to a 4-Lane Main-Link                                        | 134 |

| Table 2-78:  | 8bpp RAW Mapping to a 2-Lane Main-Link                                        | 134 |

| Table 2-79:  | 8bpp RAW Mapping to a 1-Lane Main-Link                                        |     |

| Table 2-80:  | 10bpp RAW Mapping to a 4-Lane Main-Link                                       | 135 |

| Table 2-81:  | 10bpp RAW Mapping to a 2-Lane Main-Link                                       | 135 |

| Table 2-82:  | 10bpp RAW Mapping to a 1-Lane Main-Link                                       | 135 |

| Table 2-83:  | 12bpp RAW Mapping to a 4-Lane Main-Link                                       | 136 |

| Table 2-84:  | 12bpp RAW Mapping to a 2-Lane Main-Link                                       | 136 |

| Table 2-85:  | 12bpp RAW Mapping to a 1-Lane Main-Link                                       | 136 |

| Table 2-86:  | 14bpp RAW Mapping to a 4-Lane Main-Link                                       | 137 |

| Table 2-87:  | 14bpp RAW Mapping to a 2-Lane Main-Link                                       | 137 |

| Table 2-88:  | 14bpp RAW Mapping to a 1-Lane Main-Link                                       |     |

| Table 2-89:  | 16bpp RAW Mapping to a 4-Lane Main-Link                                       | 138 |

| Table 2-90:  | 16bpp RAW Mapping to a 2-Lane Main-Link                                       | 138 |

| Table 2-91:  | 16bpp RAW Mapping to a 1-Lane Main-Link                                       | 138 |

| Table 2-92:  | TU of 30bpp RGB Video over 2.7Gbps/lane Main-Link                             | 141 |

| Table 2-93:  | DPRX Stream Reconstruction Actions within the Sink Device                     | 145 |

| Table 2-94:  | MSA Data Fields                                                               | 149 |

| Table 2-95:  | MSA Packet Timing Parameters that Can Be Ignored                              | 153 |

| Table 2-96:  | MSA MISC1 and MISC0 Fields for Pixel Encoding/Colorimetry Format Indication . | 158 |

| Table 2-97:  | SDP Header Bytes                                                              | 159 |

| Table 2-98:  | SDP Types                                                                     | 159 |

| Table 2-99:  | Audio_TimeStamp SDP Header Bytes                                              |     |

| Table 2-100: | Audio_TimeStamp SDP Maud and Naud Value Examples (Informative)                | 163 |

| Table 2-101: | Audio High Bit Rate Mode (Informative)                                        | 165 |

| Table 2-102: | Non-HBR-encoded Audio 2-channel Layout (Informative)                          | 166 |

| Table 2-103: | Non-HBR-encoded Audio 8-channel Layout (Informative)                          | 167 |

| Table 2-104: | L-PCM Audio and L-PCM 3D Audio Modes (Informative).                           | 168 |

| Table 2-105: | One Bit and DST Audio Modes (Informative)                                     | 169 |

| Table 2-106: | Audio_Stream SDP Header Bytes.                                                | 170 |

| Table 2-107: | Audio Samples Carried By Each L-PCM 3D Audio Audio_Stream SDP                 | 175 |

| Table 2-108: | Audio_Stream SDP Payload with IEC 60958-like Coding Bit Definitions           | 185 |

| Table 2-109: | Audio_Stream SDP Payload with One Bit Audio Coding Bit Definitions            | 186 |

| Table 2-110: | Audio_Stream SDP Payload with DST Audio Coding Bit Definitions                | 187 |

| Table 2-111: | Audio_Stream SDP Coding Type Payload Capacity Summary (Informative)           | 190 |

| Table 2-112: | 32-channel L-PCM 3D Audio Mandates on DMT ID = 57h Mode (Informative)         |     |

| Table 2-113: | Extension SDP Header Bytes                                                    | 194 |

| Table 2-114: | Audio_CopyManagement SDP Header Bytes.                                        | 195 |

| Table 2-115: | ISRC SDP Header Bytes                                                         |     |

| Table 2-116: | VSC SDP Header Bytes                                                          |     |

| Table 2-117: | VSC SDP Payload for DB16 through DB18                                         |     |

| Table 2-118: | Camera SDP Header Bytes                                                       | 206 |

|              |                                                                               |     |

| Table 2-119: | PPS SDP Header Bytes                                                      | 9 |

|--------------|---------------------------------------------------------------------------|---|

| Table 2-120: | VSC_EXT_VESA and VSC_EXT_CTA SDP Header Bytes                             | 3 |

| Table 2-121: | VSC_EXT_VESA and VSC_EXT_CTA SDP Payload Bytes - DB0 through DB31 212     | 3 |

| Table 2-122: | Extended INFOFRAME Payload Mapping of the                                 |   |

|              | First VSC_EXT_CTA SDP Payload Bytes – DB0 through DB31                    | 5 |

| Table 2-123: | Extended INFOFRAME Payload Mapping of the                                 |   |

|              | Second VSC_EXT_CTA SDP Payload Bytes – DB0 through DB31213                | 5 |

| Table 2-124: | Adaptive-Sync SDP Header Bytes                                            |   |

| Table 2-125: | INFOFRAME SDP v1.2 Header Bytes                                           |   |

| Table 2-126: | INFOFRAME SDP v1.2 Payload Data Bytes – DB0 through DB31                  | 1 |

| Table 2-127: | INFOFRAME SDP v1.3 Header Bytes                                           | 2 |

| Table 2-128: | INFOFRAME SDP v1.3 Payload Data Bytes – DB0 through DB31                  | 2 |

| Table 2-129: | DP Source Device DP_PWR State Rules                                       |   |

| Table 2-130: | DP Sink Device DP_PWR State Rules                                         | 4 |

| Table 2-131: | DPTX AUX_CH State and Event Descriptions                                  | 6 |

| Table 2-132: | DPRX AUX_CH State and Event Descriptions                                  | 7 |

| Table 2-133: | Current_Capabilities_Structure Syntax                                     | 3 |

| Table 2-134: | Current_Capabilities_Structure Field Definitions                          | 3 |

| Table 2-135: | Bit Field Definition for S3D Capabilities                                 | 4 |

| Table 2-136: | Bit Field Definition for Color Depth Indication for RGB, Luma, and Chroma | 4 |

| Table 2-137: | DPCD Registers Used with Virtual DP Peer Devices                          | 0 |

| Table 2-138: | Summary of VC Payload Control Link Symbol Sequence                        | 7 |

| Table 2-139: | VC Payload Bandwidth for One Time Slot per MTP Allocation                 |   |

|              | for Various Link Configurations                                           | 9 |

| Table 2-140: | 8b/10b Channel Coding VC Payload ID Table                                 |   |

|              | of DPRX Mapped to DPCD Address Space                                      | 5 |

| Table 2-141: | 8b/10b Channel Coding DPCD Address Map for                                |   |

|              | VC Payload Table Update and ACT Status Verification                       |   |

| Table 2-142: | Various Events and Impacts on VC Payload ID Table                         |   |

| Table 2-143: | MTPH Control Functions                                                    | 1 |

| Table 2-144: | MTP Payload Control Functions                                             | 1 |

| Table 2-145: | Scrambled Index to K-Code Map                                             | 2 |

| Table 2-146: | 128b/132b vs. 8b/10b Channel Coding Comparison                            | 8 |

| Table 2-147: | 8b/10b Link Layer-to-128b/132b Link Layer Control Link Symbol Mapping     | 3 |

| Table 2-148: | LLCP Bit Mapping                                                          | 5 |

| Table 2-149: | 128b/132b Channel Coding VC Payload ID Table of DPRX Mapped               |   |

|              | to DPCD Address Space                                                     |   |

| Table 2-150: | 128b/132b Link Layer Per-time-slot PBN Values                             | 3 |

| Table 2-151: | Mapping of 128-bit Cipher Key Stream to 128b/132b Link Layer Lanes        | 4 |

| Table 2-152: | XOR'ing/Non-XOR'ing of LLCP with Key Stream                               | 4 |

| Table 2-153: | DP DSC Sink Device Compressed Transport Bit Rate Range                    | 1 |

| Table 2-154: | DP DSC Source Device Compressed Transport Bit Rate Range                  | 2 |

| Table 2-155: | Number of Slices Needed per Display Line                                  | 8 |

| Table 2-156: | Color Channel Mapping for RGB Color Conversion Bypass Mode                | 1 |

| Table 2-157: | DSC PPS Syntax Element Flags and Settings                                    |

|--------------|------------------------------------------------------------------------------|

|              | Needed for Enabling RGB Color Conversion Bypass Mode                         |

| Table 2-158: | DSC .cfg File Settings for RGB Color Conversion Bypass Mode                  |

| Table 2-159: | 3D Stereo Video DP DSC Transport                                             |

| Table 2-160: | DSC Support Mandate for 128b/132b Link Layer-capable DP Device Exemptions362 |

| Table 2-161: | DSC Support Mandates for a DP Source Device with                             |

|              | a 128b/132b Link Layer-capable DFP                                           |

| Table 2-162: | DSC Support Mandates for a DP Sink Device with                               |

|              | a 128b/132b Link Layer-capable UFP                                           |

| Table 2-163: | DSC Support Mandates for a DP Branch Device with                             |

|              | a 128b/132b Link Layer-capable UFP                                           |

| Table 2-164: | DP Branch Device DFP Minimum                                                 |

|              | Uncompressed Display Stream Output Mandate                                   |

| Table 2-165: | DP Branch Device DSC Decoding Resources Needed to Meet DFP Minimum           |

|              | Uncompressed Display Stream Output Mandate with 2-lane UHBR10 UFP            |

| Table 2-166: | Sequence of DSC Bitstream Bit Depth Change that Involves                     |

|              | a Time Slot Allocation Change                                                |

| Table 2-167: | DSC Extended Capability Branch Total DSC Resources                           |

|              | DPCD Registers for Figure 2-129 Configuration Example                        |

| Table 2-168: | Virtual DSC Extended Capability DPCD Register Settings                       |

|              | for Figure 2-131 Configuration Example #1                                    |

| Table 2-169: | Virtual DSC Extended Capability DPCD Register Settings                       |

|              | for Figure 2-132 Configuration Example #2                                    |

| Table 2-170: | Bit/Byte Size of Various Data Types of AUX Transaction Syntax                |

| Table 2-171: | Request Command Definition, Bit 3                                            |

| Table 2-172: | Reply Command Definition, Bits 3:0                                           |

| Table 2-173: | Request Command Definition, Bits 2:0, When Bit $3 = 0 \dots 385$             |

| Table 2-174: | I <sup>2</sup> C Write Transaction Method 1                                  |

| Table 2-175: | $I^2C$ Write Transaction Method 1 with a Slow $I^2C$ Bus in the Sink Device  |

| Table 2-176: | $I^2C$ Write Transaction Method 2                                            |

| Table 2-177: | $I^2C$ Read Transaction Method 1                                             |

| Table 2-178: | $I^2C$ Read Transaction Method 2                                             |

| Table 2-179: | $I^2C$ Write followed by an $I^2C$ Read                                      |

| Table 2-180: | Burst Write Sizes/Bus Speed Retry Limits                                     |

| Table 2-181: | Burst Read Sizes/Bus Speed Retry Limits                                      |

| Table 2-182: | DPCD Field Address Mapping                                                   |

| Table 2-183: | Address Mapping within DPCD Receiver Capability Field                        |

|              | (DPCD Addresses 00000h through 000FFh)427                                    |

| Table 2-184: | Address Mapping within DPCD Link Configuration Field                         |

|              | (DPCD Addresses 00100h through 001FFh)467                                    |

| Table 2-185: | Address Mapping within DPCD Link/Sink Device Status Field                    |

|              | (DPCD Addresses 00200h through 002FFh)                                       |

| Table 2-186: | Address Mapping within DPCD Source Device-specific Field                     |

|              | (DPCD Addresses 00200h through 003FFh)                                       |

| Table 2-187: | Address Mapping within DPCD Sink Device-specific Field                       |

|              | (DPCD Addresses 00400h through 004FFh)515                                    |

|                                                                                                                                                                                                                                                     | Address Mapping within DPCD Branch Device-specific Field                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                       |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                                     | (DPCD Addresses 00500h through 005FFh)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                       |

| Table 2-189:                                                                                                                                                                                                                                        | Address Mapping within DPCD Link/Sink Device Power Control Field                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | c 1 7                                                                                                                                                                                                                                                                                                 |

| <b>T</b> 11 <b>A</b> 100                                                                                                                                                                                                                            | (DPCD Addresses 00600h through 006FFh)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                       |

| Table 2-190:                                                                                                                                                                                                                                        | Address Mapping within DPCD eDP-specific Field                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | <b>510</b>                                                                                                                                                                                                                                                                                            |

| T 11 2 101                                                                                                                                                                                                                                          | (DPCD Addresses 00700h through 007FFh)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                       |